지멘스 워크플로우 소프트웨어와 SPIL IC 패키징 기술 협력

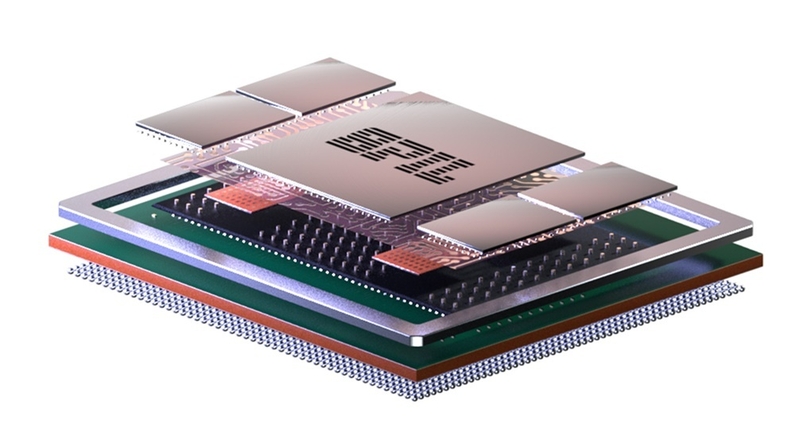

지멘스 패키지 플래닝 및 팬아웃 솔루션과 SPIL 팬아웃웨이퍼레벨패키지(FOWLP)의 기술적 협력이 새로운 반도체 조립 공정을 탄생시켰다.

산업 발전에 따른 기술 고도화 요구가 날로 증가하고 있는 지금, 반도체 산업에서도 소형화·경량화·효율화 바람이 불고 있다. 이에 지멘스와 SPIL이 기술 협력을 통해 IC 패키지 어셈블리 플래닝 최신화 및 3D LVS(Layout versus Schematic) 어셈블리 워크플로우 개발 및 상용화 준비를 마쳤다.

A.J. 인코르바이아(A.J. Incorvaia) 지멘스 EBS(Electronic Board Systems) 부문 부사장은 “지멘스는 SPIL과 협력해 SPIL 첨단 패키징 기술에 적용될 워크플로우 및 기술을 제공하게 됐다”며 “SPIL 고객이 복잡한 설계를 개발하는 데 필요한 첨단 워크플로우를 제공할 준비를 갖추고 있다”라고 말했다.

이번에 양사가 협력해 개발한 워크플로우에는 지멘스 Xpedition Substrate Integrator·Calibre 3DSTACK 등 소프트웨어와 SPIL 팬아웃웨어퍼레벨패키지(FOWLP) 등 기술이 활용됐다. 새로운 워크플로우는 패키지 플래닝 및 첨단 팬아웃 라인업의 3D 패키지 어셈블리 검증 LVS에 적용됐다.

해당 워크플로우는 정교한 IC 설계·첨단 패키징 기술 적용 등에 활용될 전망이다. SPIL은 향후 2.5 및 팬아웃 패키지 제품군 생산에 해당 워크플로우를 적용할 계획이라고 밝혔다.

주 보 완(Yu Po Wang) SPIL CRD 부문 부사장은 “우리 해결 과제는 검증된 첨단 패키징 어셈블리 플랜 및 검증 워크플로우를 개발해 적용하는 것이었다”며 “지멘스의 입증된 워크플로우를 보유한 기업으로, 지멘스 기술을 자사 팬아웃 제품군 기술 검증에 활용할 것”이라고 말했다.

헬로티 최재규 기자 |