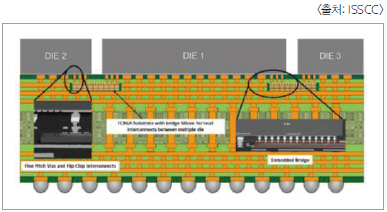

인텔(Intel)이 지난 2월 5일~9일까지 미국 캘리포니아 주 샌프란시스코에서 개최된 ‘ISSCC 2017’에서 자사의 차세대 FPGA ‘Stratix X’에 관한 논문을 발표하고, 2.5D(2.5차원) 패키징 바꾸는 저비용의 대체 기술에 대한 세부 사항을 공개했다. Stratix X는 인텔 자체의 EMIB(Embedded Multi-die Interconnect Bridge) 기술을 사용해 FPGA를 4개의 트랜시버와 연결하고 있다.

실리콘 다이에서 만든 브릿지를 BGA 기판에 탑재한 것으로, TSMC가 개발한 ‘CoWoS(Chip on Wafer on Substrate) 프로세스’로 사용되고 있는 실리콘 기판에 비해 대폭적인 소형화에 성공했다. CoWoS 프로세스는 인텔의 라이벌 인 FPGA 벤더 자일링스(Xilinx)와 GPU 벤더 엔비디아(NVIDIA)에도 채용되고 있다. EMIB 기술은 55μm의 마이크로 범프와 100μm이상의 플립 칩 범프를 조합해 사용함으로써 각각 96개의 I/O를 탑재한 트랜시버 채널을 최대 24개 지원할 수 있다고 한다. 전용 프로토콜을 사용해 1대당 1.2pJ/비트에서 1핀당 2G비트/초를 실현할 수 있다.

▲ EMIB 는 THV (관통 비아)를 사용하지 않고 고밀도 배선을 실현하고있다.

이 브릿지는 현재 4개의 28GHz SerDes(Serializer/Deserializer)를 FPGA에 연결하고 있다. 인텔의 엔지니어인 데이비드 그린힐(David Greenhill)은 ISSCC 2017에서 논문을 발표하고 “인텔은 SerDes 및 각종 외부 칩의 고속화 실현을 위한 로드맵을 마련하고 있다”고 말했다.

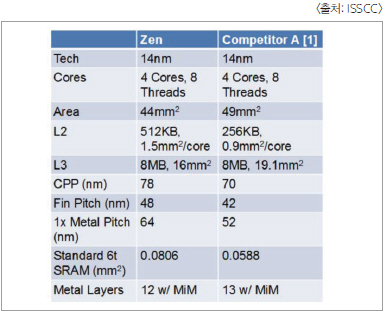

▲ AMD는 Zen이 14nm 공정을 적용한 Intel의 x86 코어보다 소형이라고했다.

이번 패키징 기술에 관한 질문에 대해 그는 “인텔의 개발팀은 56G SerDes로의 전환을 실현하는데 있어서 온도 관련 과제에 대해서도 문제없이 처리할 수 ??있다고 생각한다”고 답했다. 인텔은 2014년 9월에 파운드리 서비스의 일환으로 EMIB기술을 발표했지만, 아직 EMIB의 신규 사용자를 발표하지 않고 있다.

14nm프로세스를 적용하는 Stratix X는 기가 헤르쯔 동작의 560mm2 의 패브릭에 280만 개의 로직 엘리먼트를 탑재한다고 한다. 이와함께 AMD는 ‘ISSCC 2017’에서 자사의 x86 프로세서 ‘Zen’를 선보였다. 14nm 공정을 적용한 인텔의 최신 CPU에 비해 ??다이 크기를 10% 축소하는데 성공했다고 한다.

애널리스트 등 업계 관계자는 “Zen 코어는 매우 높은 경쟁력을 가지고 있다. 하지만 AMD에 있어서 다이 크기를 축소하는 것이 저비용화의 실현으로 이어질지는 현재 아직 밝혀지지 않은 수많은 변수에 의해서 결정될 것”이라고 말했다. 논문에 따르면, AMD가 이번에 채용한 기술은 기존 칩에 비해 스위칭 용량을 15% 줄일 수 있다. 예를 들어 Zen은 AMD에게 처음으로 MIM(metal-insulator-metal) 구조의 커패시터를 사용함으로써 동작 전압의 감소와 코어 당 공급 전압의 증가, 주파수 제어 기능의 향상 등을 실현할 수 있었다고 한다.

정가현 기자 (eled@hellot.net)