누화(CROSSTALK)

⑥ 입력 커패시터와 단일 종단 동작을 사용해 PCB 누화를 낮추다

LTC2358은 고유의 회로를 사용해서 동적 채널들 간에 극히 우수한 내부 누화 절연을 달성한다(109dB 정격). 위아래 도전층으로 접지를 사용해서 PCB 상에서 아날로그 입력으로 연결되는 배선을 차폐함으로써 채널들 간의 외부 커패시티브 누화를 최소화할 수 있다. 인접한 패키지 핀들 간의 커패시턴스는 0.16pF이다. 낮은 소스 저항과 높은 소스 커패시턴스를 조합적으로 사용해서 외부적인 커패시티브 결합 누화를 줄일 수 있다. 예를 들어서 그림 13의 IN0에서는 소스 저항과 별개로 아날로그 입력으로 18nF 커패시터를 사용해서 인접 핀으로부터 유발되는 0.16pF의 커패시티브 결합을 100dB 감쇠하고 있다.

▲ 그림 13. 입력 커패시터와 낮은 소스 임피던스를 사용해서

PCB 누화를 낮출 수 있다.

낮은 소스 임피던스 역시 외부 배선 누화를 낮출 수 있다. 그림 13의 채널 IN1은 입력 커패시턴스와 별개로 100Ω(또는 그 이하) 소스 저항을 사용해서 100kHz에 이르기까지 100dB의 누화 제거를 달성하고 있다.

높은 주파수에 높은 소스 저항을 사용하고 추가적인 입력 커패시터를 사용하지 않으면 인접 핀들 간의 0.16pF 커패시턴스가 인접 채널의 입력 커패시턴스와 함께 26dB 이상의 전압 감쇠기를 형성한다. 이것은 3pF의 내부 커패시턴스에 어떠한 PCB 입력 트레이스 커패시턴스가 더해진 것이다. 소스 저항과 3pF 내부 입력 커패시턴스에 의해서 추가적인 감쇠가 제공됨으로써 DC에 이를 때까지 낮은 주파수 쪽으로 향해서 6dB/옥타브 향상이 이루어진다. DC일 때 109dB의 최대 ADC 누화 성능이 달성된다. 10k 소스 저항이라면, 입력 핀에서 10k 소스 저항과 3pF 입력 커패시턴스에 의해서 형성된 5MHz 극점 아래의 주파수들에 대해서 6dB/옥타브 경사로 결합이 감소될 것이다. 100kHz일 때 핀-대-핀 누화 제거는 0.16pF/3pF • 0.1MHz/5MHz = 0.001(–60dB)로 계산된다.

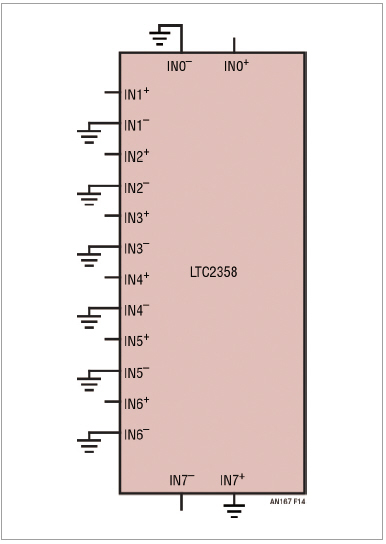

여기에 더해서 보드 입력 트레이스들 간의 추가적인 커패시턴스를 반영해야 한다. 단일 종단 입력 구동은 추가적으로 외부 누화 절연이 이루어진다는 부가적인 이점이 있다. 입력 핀들을 하나 걸러서 접지를 하고(그림 14) 또는 낮은 임피던스 DC 소스를 사용해서 구동하므로 채널들 간에 차폐 역할을 하기 때문이다. 중요한 점은, 입력 핀에 이르기까지 각 입력 배선 연결을 GND를 사용해서 완벽하게 차폐해야 한다는 것이다.

▲ 그림 14. 접지된 Inx- 입력이 외부 차폐로서 역할을 한다

범위(RANGE)

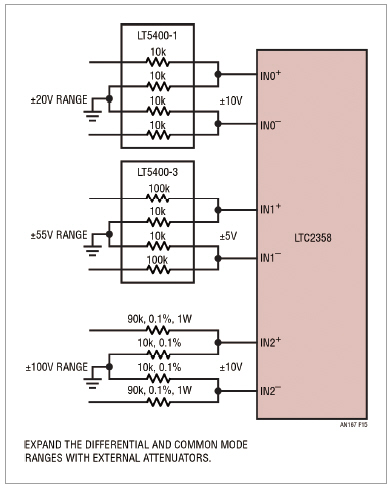

⑦ 감쇠기를 사용한 ADC 입력 범위 확장

1000GΩ 이상의 피코암페어 아날로그 입력을 제공하므로 외부 정밀 감쇠기로 더 높은 전압 입력 범위를 달성하기에 잘 맞는다. 예를 들어서 LT5400은 매칭 정확도가 0.01%인 정밀 쿼드 저항 네트워크 제품군으로서, 이 제품을 사용함으로써 최대 동작 전압인 ±75V에 이르기까지 다양한 아날로그 입력 범위를 달성할 수 있다.

그림 15의 감쇠기 회로는 임피던스가 10kΩ 아래이다. 그러므로 포착 간격이 시작될 때 내부 CMOS 버퍼를 거쳐서 채널 입력으로 피드백 되는 낮은 AC 결합 트랜션트로부터 LTC2358 입력이 완벽하게 안정화할 수 있다.

▲ 그림 15. 입력 범위 확장기

디스크리트 감쇠기에는 저항 자체 발열을 최소화하기 위해서 1W 저항이 권장된다. 이러한 발열은 저항의 온도 계수에 따라서 저항 값을 변화시킬 수 있다. 1W 저항 정격은 채널 IN2에서 100V 입력으로 90k 저항에서 소비되는 90mV보다 훨씬 큰 것이다.

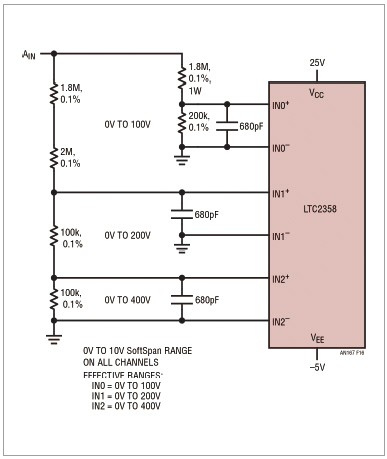

⑧외부 감쇠기를 사용한 자동 이득 레인징

그림 16은 0V~100V, 0V~200V, 0V~400V의 가능한 세 가지 전압 범위에서 1.33M의 최소한의 부하로 AIN에서 전압을 측정하기 위해서 고 임피던스 감쇠기 네트워크를 적용한 것을 보여준다. 3개 채널이 감쇠된 전압을 동시적으로 샘플링 한다. 그런 다음 디지털 채널 출력에서 모두 1로 포화되지 않는 가장 작은 범위로서 사용자가 적절한 범위를 선택할 수 있다. 어떤 채널도 모두 1로 포화되지 않으면 항상 IN0 출력으로부터의 100V 범위를 선택할 것이 권장된다. 이렇게 하면 일종의 자동 이득 레인징을 구현할 수 있다.

▲ 그림 16. 자동 이득 레인징

AIN의 전압이 250V로 상승하면 IN0+의 ESD 보호 다이오드가 포워드 바이어스를 시작하고, AIN = 400V일 때 최대 80μA까지 전도한다. 이와 같은 IN0+의 과구동은 다른 채널들에 영향을 미치지 않는다. 아날로그 채널 입력 과구동에 관해서는 3절(전자기술 10월호 42p)을 참조한다.

이 네트워크의 MΩ 임피던스가 가능한 것은 매우 낮은 아날로그 입력 누설(5pA 정격) 때문이다. 이 MΩ 임피던스를 선택한 것은 외부 소스로 부담을 최소화하고 0.1% 감쇠기 입력 저항의 전력 소모를 최소화하기 위해서다. 아날로그 채널 입력에서 680pF 필터 커패시터는 포착 간격이 시작될 때 내부 CMOS 버퍼 피드쓰루 글리치를 억제하고 외부 잡음을 여과한다. 채널 입력의 실온 누설이 5pA 정격이므로, 200kΩ 미만 감쇠기 출력으로 미미한 1μV 오프셋만을 일으킨다. 하지만 누설 전류는 온도에 따라서 지수적으로 상승하므로 85℃에서 최대 500pA까지 이를 수 있다는 점에 유의해야 한다. 임피던스가 이보다 낮은 네트워크를 사용함으로써 고온으로 누설 전류의 영향을 낮출 수 있다. 또 아니면 비반전 채널 입력의 임피던스와 일치하게 접지된 반전 채널 입력으로 직렬로 저항을 추가함으로써 고온으로 증가된 입력 바이어스 전류로 인해서 발생되는 오프셋 전압을 어느 정도 제거할 수 있다. 이들 저항 역시 동적 입력에 사용된 것과 같은 값의 추가적인 필터 커패시터를 사용해서 바이패스해야 한다.

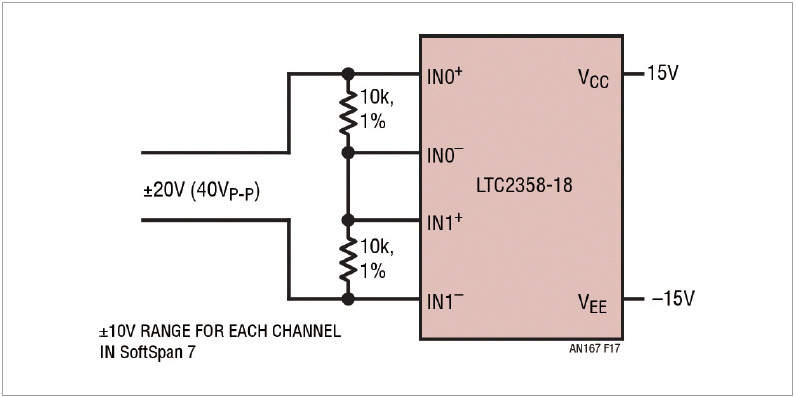

⑨ 입력 범위를 ±20V(40VP-P)로 두 배로 높이고, SNR을 99dB로 높이다.

LTC2358은 VCC – VEE = 38V로 최대 30VP-P에 이르기까지 공통 모드 범위가 매우 넓을 뿐만 아니라 공통 모드 제거가 최소 100dB로 극히 우수하므로 아날로그 입력을 성능 저하 없이 원하는 대로 구동할 수 있다.

예를 들어서 어떠한 2개 채널을 직렬로 합침으로써 입력 범위를 두 배로 하고 SNR을 3dB 향상시킬 수 있다. 2개 채널의 출력 코드를 더해 또 하나의 순수한 결과값을 발생시킴으로써 추가적인 비트의 분해능을 제공할 수 있다. 다시 말해서 LTC2358-16을 사용하면 17비트 분해능을, LTC2358-18을 사용하면 19비트 분해능을 제공할 수 있다.

CNV의 상승 에지인 샘플링 순간에 동시적인 샘플링이 2개 채널이 동기화되도록 한다. 저항의 정확도는 이 합쳐진 조합의 이득에 영향을 미치지 않는다. 한 채널에서 저항 매칭 오차로 인해서 존재하는 어떠한 여분의 신호가 합쳐진 다른 채널로부터 정확하게 감해지기 때문이다. 10k + 10k 전압 분할기의 불일치로 인한 영향은 풀 스케일에 가까워졌을 때 한 채널이 다른 채널보다 앞서서 포화된다는 것뿐이다. 이렇게 합쳐진 조합의 범위는 ±20.48VP-P • (1 – VDE)이다. 이 공식에서 VDE는 전압 분할기 오차이다.

예를 들어서 0.1% 전압 분할기 오차이면 VDE = 0.001이다. 전압 값이 이상적인 합계 풀 스케일의 VDE 이내에 도달해감에 따라서, 한 채널이 포화해서 전압 범위가 이득 기울기가 절반이 되고 두 번째 채널이 포화함에 따라서 합계 출력이 완전히 포화한다. 대다수 애플리케이션에서는 작은 감쇠 오차에 의해서 피크-대-피크 합계 범위가 축소되더라도 별 영향을 받지 않을 것이다. 합계 이득이 영향을 받지 않고 합쳐진 2개 채널의 평균 이득 오차와 동일할 것이기 때문이다.

저잡음 저-드리프트 고정밀 레퍼런스로서 LTC6655-5 외부 5V 레퍼런스를 사용해서 내부 4.096V REFBUF 핀을 과구동하면 아날로그 입력 범위를 추가적으로 더 확장하는 것도 가능하다. 각 채널의 아날로그 입력 범위가 ±10.24V에서 ±12.5V로 레퍼런스와 동일한 비율로 확장된다. LTC2358-18과 외부 5V 레퍼런스를 사용하면 합쳐진 ±25V 범위는 SNR = 100dB이다. 외부 레퍼런스로서 LTC6655-5V를 배선하는 것에 관해서는 LTC2358 데이터 시트의 “Application Information” 부분을 참조한다.

그림 17에서 10k 저항을 정밀 저항으로 대체하고 8절에서처럼 정밀 감쇠기를 구현하면 이 회로를 추가적으로 더 넓은 전압 범위로 확장할 수 있다.

▲ 그림 17. 입력 범위를 ±20V(40VP-P)로 두 배로 높이고, SNR을 99dB로 높인다.

필터(FILTER)

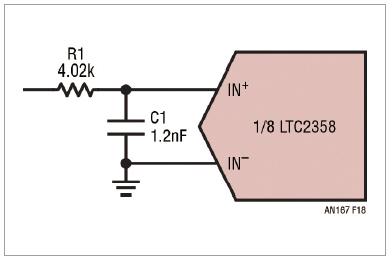

⑩ kΩ 임피던스의 능동 또는 수동 필터를 사용해서 LTC2358을 직접 구동

ADC의 아날로그 입력 앞에서는 에일리어싱 방지 및 잡음 필터를 매우 일반적으로 사용한다. LTC2358의 아주 높은 입력 임피던스(>1000GΩ) 피코암페어 아날로그 입력은 다양한 유형의 RC 수동 필터 조합을 사용해서 손쉽게 구동할 수 있다. 그러므로 버퍼 기능을 포함하지 않는 통상적인 ADC를 사용할 때처럼 까다로운 구동 요구에 맞출 필요 없이 아날로그 신호를 필터링하도록 손쉽게 최적화할 수 있다.

데이터 시트에서 권장하고 있듯이, 아날로그 입력으로 680pF 혹은 그 이상의 커패시터를 사용해서 포착 간격이 시작될 때 샘플링 프로세스로부터 내부 버퍼를 통해서 피드백되는 아주 작은 AC 트랜션트를 흡수할 수 있다. 그럼으로써 포착 간격 이내에 안정화하지 못하는 10kΩ 이상의 소스 임피던스로 LTC2358의 DC 정확도를 유지할 수 있다. 이 아주 작은 글리치 역시도 전하를 띤다. 그러므로 순수하게 AC 결합을 하고, 글리치의 총 전하가 0이 되고, 어떤 DC 성분을 갖지 않는다. 외부 커패시터를 사용해서 편리하게 간단한 RC 필터를 구현함으로써 디지털화하고자 하는 아날로그 신호로부터의 잡음을 낮출 수 있다.

예를 들어서 그림 18에서처럼 R = 4.02kΩ 및 C = 1200pF을 사용해서 33kHz 저역 통과 RC 필터를 구현할 수 있다. C를 680pF으로 그대로 두거나 또는 더 높은 커패시턴스를 사용하면서 R 값을 높이거나 낮춤으로써 다른 대역폭들을 구현할 수 있다.

▲ 그림 18. kΩ 임피던스를 사용한 단일 극점 33kHz RC 필터

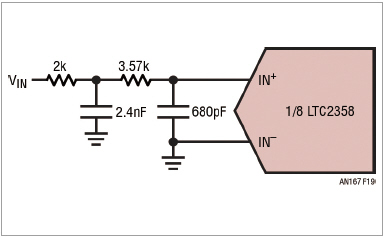

MHz 대의 고주파 간섭이 문제가 될 때는 더 높은 주파수로 추가적이고 연쇄적인 실수 극점을 사용함으로써 이러한 간섭을 효과적으로 억제할 수 있다. 이차 RC 필터는 더 높은 임피던스를 사용함으로써 일차 RC 필터로의 부담을 줄일 수 있다. 그림 19의 예에서는 일차 RC 극점은 2k와 2.4nF을 사용해서 33kHz이고 이차 RC 극점은 3.57k와 680nF을 사용해서 66kHz인 경우를 보여준다. 그리고 부하 효과에 의해서 극점이 23kHz 및 94kHz로 밀려난다. 그러므로 1MHz에서 간섭적인 10mV 톤이 33kHz의 하나의 극점만을 사용할 때는 30dB 및 33kHz와 66kHz의 2개 극점을 사용할 때는 53dB 감쇠되어서 단 22μV가 된다.

▲ 그림 19. 2극점 33kHz 및 66kHz RC 필터를 사용해서 MHz 대 간섭을

낮출 수 있다.

외부 간섭 주파수가 ADC 샘플링 속도에 근접하거나 광대역 센서 잡음이 존재하면 신호를 깨끗하게 하기 위해서 고차수 필터가 가장 효과적이다. 그림 20은 단일 극점 33kHz 필터와 3극점 33kHz 셀런-키(Sallen-Key) 능동 필터를 비교하고 있다. 이 능동 필터의 더 가파른 주파수 응답은 10mV 190kHz 간섭 주파수를 아주 효과적으로 제거하며 또한 100kHz 아래의 대역내 잡음을 더 효과적으로 감소시킨다.

능동 필터 또한 LTC2358의 버퍼드 입력을 활용할 수 있다. 이 셀런-키 능동 필터 회로에서는 LT1351 연산 증폭기가 DC 신호 경로 밖에 머물면서 간단히 능동 AC 피드백을 제공해서 AC 응답을 형성한다. 그러므로 이 연산 증폭기는 정지점 가까이에서 AC 응답이 우수해야 한다. 연산 증폭기 피드백의 대부분은 필터의 정지점 가까이에서 일어난다. 그럼으로써 연산 증폭기의 DC 전압 오차와 저주파수 전압 잡음이 신호 경로 바깥에 머문다. LT1351 연산 증폭기의 DC 입력 누설 전류는 50nA(최대)이고 3.39k 총 필터 저항으로 170μV 이내로 강하한다.

필터 애플리케이션에는 선형성과 정밀도 면에서 C0G 세라믹 또는 박막 커패시터가 권장된다. X7R 및 X5R 세라믹 커패시터는 피해야 한다. 허용오차가 좋지 않고 전압 계수가 높아서 신호 경로로 비선형성과 왜곡을 유발하기 때문이다.

Joe Sousa · Andrew Thomas, Clement Wagner of Analog Devices, Inc.

Mark Thoren, Design and Application Engineers, Linear Technology, now part of Analog Devices, Inc.