실리콘랩스의 4세대 DSPLL 아키텍처에는 아날로그 기술과 디지털 기술의 장점이 결합돼 있다. 이 아키텍처는 위상 잡음이 낮은 아날로그 LC-VCO, 디지털 PLL 아키텍처, 첨단 55nm CMOS 기술을 결합함으로써 기존의 캐시케이드 PLL 디바이스에 비해 집적도를 높이고 폼팩터를 소형화하며, 더 적은 전력을 소모한다. 이에 따라 스몰셀, 피코셀, 마이크로셀, 점대점 무선 장비, 모바일 백홀 장비의 설계를 크게 간소화한다.

모바일 네트워크 사업자들은 유효범위(Coverage)를 확장하고, 용량을 증가시켜 트래픽 양이 많은 혼잡한 대도시 환경에서 밀집된 네트워크를 구축할 수 있는 스몰셀(Small Cell) 기지국으로 눈을 돌리고 있다.

스몰셀은 저전력 무선 액세스 노드로, 사업자들이 IP(Internet Protocol) 네트워크에 대한 모바일 데이터 부담을 덜고 4G/LTE 애플리케이션에서 무선 스펙트럼을 좀 더 효율적으로 활용할 수 있게 한다. 스몰셀은 서비스 사업자들이 폭발적으로 늘어나는 대역폭 요구를 충족할 수 있도록 중요한 역할을 수행하고 있다.

그러나 그 이점을 최대한 실현하기 위해 스몰셀은 크기, 전력, 성능, 비용 측면에서 최적화되어야 한다. 최적화 기법이 중요한 이유는, 스몰셀이 설치되는 곳이 공간 제약적이고 밀집적이며 온도를 제어할 수 없는 옥외 환경에 있기 때문이다.

또한 스몰셀은 흔히 PoE(Power over Ethernet)를 사용해서 작동하므로 전력 소모를 최소화해야 한다. 지금까지는 하나의 칩(SoC)에 베이스밴드 시스템과 디지털 무선 프론트엔드의 통합을 최적화하기 위해 많은 노력을 기울여 왔다. 여기서는 스몰셀 설계 시 숙고해야 할 측면으로, 타이밍과 클록 합성에 대해 살펴본다. 새로운 IC 아키텍처를 사용함으로써 스몰셀로 더 적은 전력을 소모하고 폼팩터를 소형화하며 더 높은 성능을 달성하는 클록 합성이 가능해졌다.

위상 잡음이 낮은 정수-N PLL을 구현하기 위한 아키텍처

스몰셀 애플리케이션에 사용하도록 위상 잡음이 낮은 정수-N PLL을 구현하는 칩 아키텍처에는 두 가지 기법이 있을 수 있다.

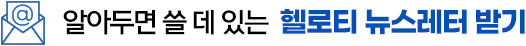

그림 1은 기존의 아날로그 아키텍처를 사용해서 무선 인프라 애플리케이션에 사용하기 위한 지터 감쇠 PLL(Phase-Locked Loop)을 구현하는 것이다. 두 가지 단계의 캐시케이드 PLL 아키텍처에서는 첫 번째 루프로 디스크리트 아날로그 협대역 VCXO(Voltage-Controlled Crystal Oscillator) 기반 PLL을 사용해 지터 클리닝을 구현하고 있다.

위상 잡음이 낮다는 점에서 VCXO를 PLL VCXO로 사용하고 있다. 2단계 PLL은 아날로그 광대역 PLL을 사용해서 클록 곱셈을 수행한다. 따라서 이러한 기존 아키텍처는 디스크리트 VCXO에 더해 디스크리트 루프 필터 소자를 필요로 한다.

▲ 그림 1. 캐시케이드 PLL 아키텍처

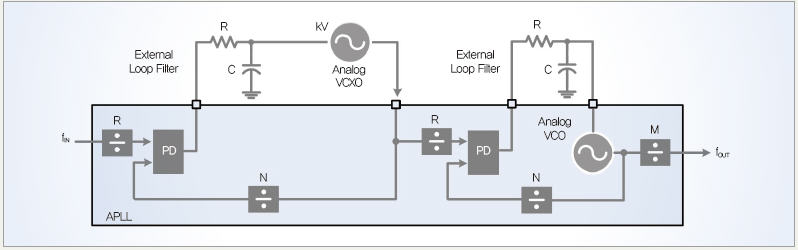

그림 2는 실리콘랩스의 4세대 DSPLL 아키텍처를 사용한 대안적 기법을 나타낸 것이다. DSPLL은 내곽 루프와 외곽 루프로 이루어진 듀얼 루프 PLL 아키텍처를 사용해서 저대역폭 지터 감쇠 PLL을 구현한다. 내곽 루프가 외곽 루프의 디지털 제어 오실레이터(DCO)로 동작한다.

▲ 그림 2. DSPLL 듀얼 루프 아키텍처

내곽 루프는 위상 잡음이 낮은 15GHz 아날로그 LC 오실레이터를 기반으로 한 광대역 PLL이다. VCO를 아날로그 회로로 제어하는 것이 아니라, 고분해능 분수-N 피드백 분할기를 사용해서 디지털적으로 제어할 수 있다. 분수-N 피드백 분할기를 정밀한 간격으로 조절할 수 있으므로 전체적인 내곽 루프가 DCO로 동작할 수 있다.

LC 오실레이터는 튜닝 범위가 넓어지므로 내곽 루프 PLL은 넓은 주파수 범위로 동작할 수 있다. 저가격대의 기본 모드 ‘non-pullable’ 크리스털을 내곽 루프 레퍼런스로 사용한다. 루프 필터 기능을 디지털적으로 구현함으로써 디스크리트 소자가 필요 없다.

DSPLL 외곽 루프는 외부적으로 제공되는 레퍼런스 클록으로 동기화, 지터 감쇠, 클록 곱셈의 세 가지 기능을 수행한다. 내곽 루프를 디지털적으로 제어하는 것과 마찬가지로, DSPLL 외곽 루프 역시 고도로 디지털적인 아키텍처를 사용해서 구현할 수 있다. DSPLL 외곽 루프 필터를 첨단 아날로그-디지털 컨버터(ADC)와 디지털 신호 프로세싱(DSP) 기반 아키텍처를 사용해 전적으로 온칩으로 구현함으로써 PCB 레이아웃과 설계를 간소화하고 보드 레벨 잡음에 대한 내구성을 극대화한다.

이 아키텍처의 또 다른 이점은 PLL 루프 대역폭 같은 주요 PLL 파라미터들을 사용자가 프로그램할 수 있다는 것이다. 이 아키텍처는 유효 주파수 튜닝 분해능이 1ppt(part-per-trillion)이기 때문에 매우 정밀한 PLL 제어가 가능하다.

따라서 각각 다른 입력 및 출력 주파수와 루프 대역폭을 지원하기 위해 BOM(Bill of Materials) 변경을 필요로 하지 않는다.

DSPLL 위상 잡음 최적화

실리콘랩스의 DSPLL 아키텍처는 지난 15년 동안 지속적으로 개선되고 향상되어 온 결과이며, 고속 데이터 컨버터와 10/40/100G 트랜시버에 사용하도록 위상 잡음이 매우 낮은 클록을 제공한다. 이 아키텍처는 아날로그 기술과 디지털 기술을 결합함으로써 최상의 집적도와 성능을 달성하고 있다.

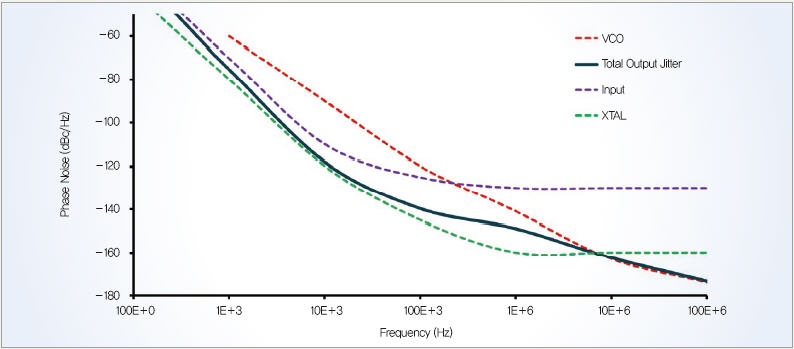

그림 3은 실리콘랩스의 4세대 DSPLL이 어떻게 위상 잡음을 최적화하는지 나타낸 것이다. 이 예에서는 모든 주파수를 1GHz로 정규화하고 있다. 기저대역 오프셋 주파수일 때 DSPLL 아키텍처의 위상 잡음이 내곽 루프의 레퍼런스로 사용된 크리스털을 바짝 뒤쫓고 있다는 것을 알 수 있다.

DSPLL 아키텍처는 기저대역 위상 잡음이 우수한 저가의 기본 모드 non-pullable 크리스털을 사용한다. 높은 오프셋일 때는(∼1MHz) DSPLL 위상 잡음이 전압 제어 오실레이터(VCO)의 뒤를 따르고 있다. 실리콘랩스의 4세대 DSPLL 아키텍처는 타이밍 업계에서 앞선 CMOS 프로세스 노드(55nm CMOS)를 이용하여 제조된 극저 위상 잡음 LC 오실레이터를 사용, 높은 오프셋 주파수로 매우 낮은 위상 잡음을 달성한다. DSPLL 출력에서 이와 같은 위상 잡음(도표에서 짙은 파란색 실선)은 이 점들이 종합적으로 작용된 것이다.

▲ 그림 3. DSPLL 위상 잡음 최적화

DSPLL의 루프 대역폭을 개발자가 디지털적으로 프로그램할 수 있으므로 레퍼런스 클록 지터를 필터링하고자 하는 지점을 설정할 수 있다(그림 3에서는 ∼1kHz). 입력이 기저대역 오프셋 주파수로 위상 잡음이 비교적 낮을 경우 좀 더 높은 DSPLL 루프 대역폭을 권장한다. 그리고 기저대역 위상 잡음이 높다면 좀 더 낮은 DSPLL 루프 대역폭이 바람직할 것이다. DSPLL 루프 대역폭을 프로그램할 수 있으므로, 고객이 지터 전달과 지터 발생을 절충적으로 최적화하고 입력 조건에 따라서 위상 잡음을 최소화하도록 할 수 있다.

DSPLL 아키텍처의 이점

단일 오실레이터 DSPLL 아키텍처는 기존의 2-오실레이터 아날로그 캐시케이드 PLL 아키텍처에 비해 우수한 통합성과 유연성을 제공한다.

두 아키텍처는 지터 감쇠, 클록 곱셈 등의 기능 면에서는 거의 비슷하지만 PCB 풋프린트, 전력 소모, 성능에는 큰 차이가 있다.

PCB 풋프린트

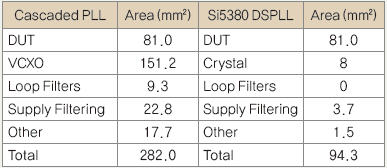

표 1은 두 아키텍처의 PCB 풋프린트를 비교한 것이다. 단, 이 비교는 PCB 간격이나 설계 규칙을 고려하지 않고 소자들의 면적만 합한 것이다. DSPLL PCB 풋프린트가 캐시케이드 PLL에 비해 3배까지 더 작다는 것을 알 수 있다.

▲ 표 1. DSPLL 아키텍처는 캐시케이드 PLL에 비해 PCB 면적 66% 감소

DSPLL은 대형 VCXO를 필요로 하지 않으므로, PCB 레이아웃과 설계를 간소화하고 총 솔루션 비용을 최소화한다. 또한 DSPLL은 루프 필터를 온칩으로 통합함으로써 PCB 레이아웃을 추가적으로 더욱 더 간소화한다.

그리고 다중의 온칩 전압 레귤레이터를 사용해서 보드 레벨 전원 잡음을 필터링하므로 필요한 디스크리트 필터링 소자를 최소화한다. 이에 비해서 캐시케이드 PLL은 좀더 많은 전용적인 전원들을 필요로 하고 이들 각각으로 각기 필터링을 필요로 한다.

DSPLL 기반 제품은 LDO(Low Drop-out) 레귤레이터를 필요로 하지 않는데, 캐시케이드 PLL은 VCO가 잡음 유입에 민감하므로 전원 필터링을 위해 외부적인 LDO가 필요하다. 그러므로 DSPLL 아키텍처의 소형 풋프린트는 스몰셀, 피코셀, 모바일 백홀과 같은 공간 제약적인 애플리케이션에 적합하다고 할 수 있다.

전력 소모

캐시케이드 PLL과 DSPLL 기반 클록 디바이스는 전력 소모에 큰 차이가 있다.

표 2는 두 기법의 전력 소모를 나타낸 것이다. 고유의 디지털 DSPLL 아키텍처가 아날로그 PLL 기반 캐시케이드 PLL 디바이스에 비해 30% 더 적은 전력을 소모하므로 전력 효율이 뛰어나다는 것을 알 수 있다.

▲ 표 2. DSPLL은 캐시케이드 PLL에 비해 전력을 30%까지 절약

실리콘랩스의 4세대 DSPLL 기반 제품은 타이밍 업계에서 가장 앞선 프로세스 기술(55nm CMOS)을 사용하며, 효율적인 디지털 집중 아키텍처를 결합함으로써 기존 솔루션에 비해 전력을 훨씬 더 절약해 준다.

전력 효율적인 아키텍처는 PoE를 사용하므로 전력 예산이 제한적인 스몰셀이나 피코셀 같은 애플리케이션에서 특히 중요하다고 할 수 있다.

위상 잡음 성능

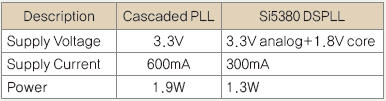

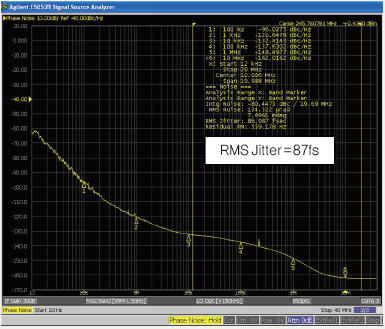

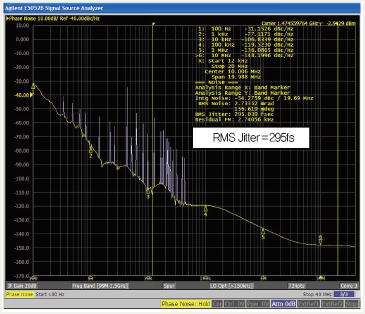

캐시케이드 PLL은 디스크리트 VCXO를 사용해서 뛰어난 위상 잡음 및 지터 성능을 달성한다(그림 4). 그러나 이러한 솔루션은 보드 레벨 잡음에 더 취약하다. 차지 펌프 출력, 루프 필터, VCXO를 비롯해 아키텍처 내의 모든 디스크리트 노드가 잡음을 유입하는 지점이 될 수 있기 때문이다.

▲ 그림 4. 캐시케이드 PLL의 위상 잡음 성능 (245.76MHz 반송파)

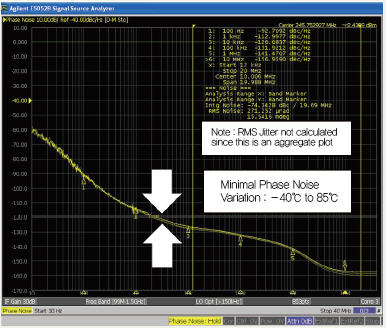

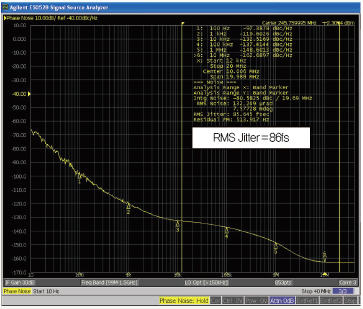

DSPLL 아키텍처는 디스크리트 VCXO, 루프 필터, LDO를 필요로 하지 않으면서 캐시케이드 PLL+VCXO 구성보다 더 우수한 위상 잡음 성능을 달성한다(그림 5). 그리고 부가적인 이점으로, DSPLL 기반 제품은 아키텍처가 통합적이므로 보드 레벨 잡음에 대해 내구성이 뛰어나다.

▲ 그림 5. DSPLL의 위상 잡음 성능 (245.76MHz 반송파)

DSPLL 아키텍처의 또 다른 이점은 온도에 대해 성능이 극히 일관적이라는 점이다. 그림 6은 -40℃, 0℃, 85℃일 때 DSPLL 아키텍처의 위상 잡음을 보여준다.

스몰셀 및 중계기 애플리케이션에서는 일관된 위상 잡음 성능이 중요하다. 왜냐하면 이들 장비가 통상적으로 온도가 제어되지 않는 환경에 설치되기 때문이다. 그림 6은 DSPLL의 입력으로 지터가 심한 레퍼런스 클록을 사용했다고 가정한 것이다.

▲ 그림 6. DSPLL의 온도에 따른 위상 잡음 성능 (245.76MHz 반송파)

루프 필터 통합 및 지터 감쇠 조절 가능

캐시케이드 PLL은 PLL1과 PLL2에 외부 루프 필터가 필요하다. 이러한 소자들은 오프칩이므로 PLL로 보드 레벨 잡음이 유입될 수 있으며 지터와 위상 잡음에 영향을 미칠 수 있다. 반면에, DSPLL 아키텍처는 루프 필터를 온칩으로 통합하고 있으므로 보드 레벨 잡음에 대해 내구성이 뛰어나다.

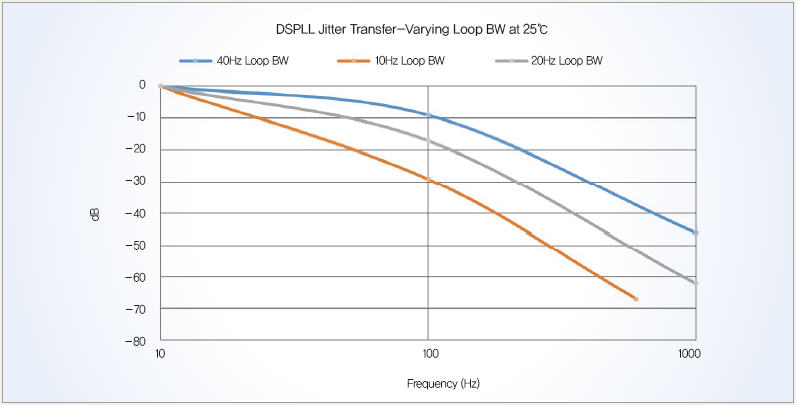

또한 캐시케이드 PLL 디자인은 PLL 대역폭이 고정적이다. 디스크리트 아키텍처이므로 PLL 대역폭을 변경하는 유일한 방법은 루프 필터 소자값을 변경하는 것이다. 따라서 애플리케이션 차원에서 지터 감쇠를 최적화하기 위해 PLL 대역폭을 세밀하게 조절하는 것이 어렵다. 이와 달리 DSPLL은 외곽 루프 대역폭을 외부적인 BOM 변경 없이 레지스터로 간편하게 프로그램할 수 있다.

그림 7은 DSPLL 루프 대역폭을 낮춤으로써 레퍼런스 클록 지터 감쇠를 어떻게 높일 수 있는지 나타낸 것이다. 루프 필터 소자값이나 PLL의 위상 마진을 계산할 필요 없이 레지스터를 통해 루프 대역폭을 간편하게 프로그램할 수 있으므로 설계 작업을 간소화한다.

▲ 그림 7. DSPLL은 지터 감쇠를 조절할 수 있다

지터 전달

협대역 PLL은 입력에서 PLL 동기화를 잃지 않으며 상당한 지터를 허용해야 하고, 레퍼런스 클록으로부터 잡음을 필터링하고 출력에 전달되는 지터를 최소화해야 한다. 이 점은 CPRI(Common Public Radio Interface)나 CPRI over OTN과 같이 협대역 PLL을 CDR(Clock and Data Recovery) IC에서의 라인 복구 클록으로 동기화하는 애플리케이션에서 특히 중요하다.

PLL의 지터 전달 함수는 인가된 입력 지터 스펙트럼에 대한 출력 지터 스펙트럼의 비이다. 잘 설계된 고성능 PLL은 PLL 대역폭에서 피크를 이루는 낮은 지터와 온도에 대해 일관된 동작을 나타낸다.

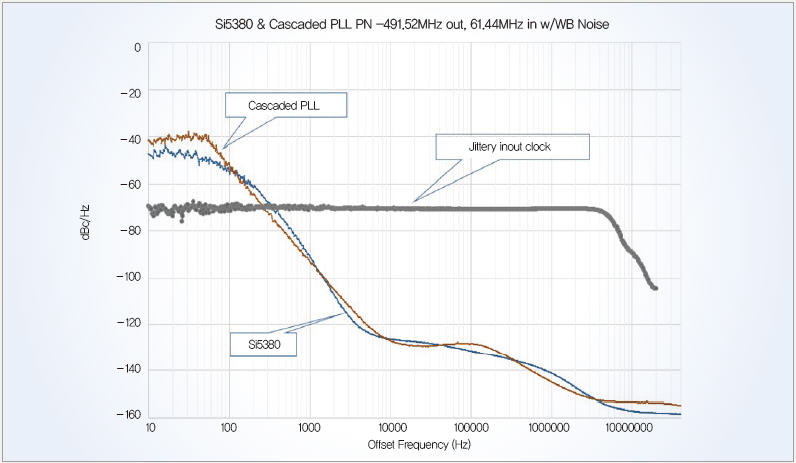

그림 8과 같이 DSPLL은 지터가 높은 입력 클록으로 동기화했을 때 캐시케이드 PLL에 필적하는 지터 전달 성능을 달성한다는 것을 알 수 있다. 그런데 또 DSPLL은 사용자가 디지털적으로 프로그램할 수 있어 뛰어난 루프 대역폭 유연성을 제공하므로, PCB를 제조한 후에도 사용자가 지터 성능을 최적화할 수 있다.

▲ 그림 8. DSPLL은 거의 비슷한 지터 전달 성능을 달성하면서 루프 대역폭 구성 유연성까지 제공한다

또한 DSPLL 아키텍처는 온도에 대해 일관적인 성능을 제공하므로(그림 6) 동작 조건에 대해 반복적으로 한결같은 성능을 보여준다. 뛰어난 지터 전달 성능은 HetNet 네트워크 구현을 간소화하는데, 스몰셀과 피코셀을 지원 인프라로부터 훨씬 멀리까지 설치할 수 있기 때문이다.

순간 홀드오버

고성능 PLL은 타이밍 동기화 체인을 구동하는 상위 PLL에 문제가 있어도 안정적이면서 정확한 출력 클록을 제공할 수 있어야 한다. 상위 PLL에 문제가 있어서 클록이 소실되면 하위 PLL이 홀드오버로 전환해 상위 PLL의 클록이 되살아날 때까지 정확한 출력 클록을 제공해야 한다. 이때 캐시케이드 PLL의 출력 클록 정확도는 상당 부분 VCXO를 얼마나 엄밀하게 유지하느냐에 달려 있다.

캐시케이드 PLL은 통상적으로 온칩 디지털-아날로그 컨버터(DAC)를 사용해서 최종 제어 전압 설정으로 VCXO를 구동한다. 하지만 이 방법으로는 VCXO를 유지하기가 어렵다. 이 방법은 특성적으로 아날로그이고 높은 초기 주파수 오프셋 오차의 영향을 받으며, 누설과 시간에 따른 주파수 드리프트에 취약할 수 있기 때문이다.

반면에 DSPLL 아키텍처는 홀드오버 주파수로 평균화 입력 클록 주파수를 사용함으로써 입력 클록이 갑자기 소실됐을 때 출력 클록 주파수의 외란을 최소화한다. 저장된 주파수 데이터 이력 중 프로그램된 범위 내의 것을 사용해서 최종적인 평균 홀드오버 주파수 값을 계산한다. 이 범위의 크기와 지연시간 모두 다 프로그램할 수 있다. 이 기능을 사용하면 홀드오버 회로로 하여금 입력 클록이 결함을 일으키기 바로 직전에 훼손됐을지도 모르는 주파수 데이터를 무시하도록 할 수 있다.

또 다른 부가적인 이점으로, DSPLL이 홀드오버에서 빠져나온 새로운 입력 클록으로 동기화를 재획득했을 때 풀링 프로세스가 글리치 없이 일어날 수 있고, DSPLL의 외곽 루프 대역폭으로 제어됨으로써 갑작스러운 주파수 편이가 발생되지 않도록 한다.

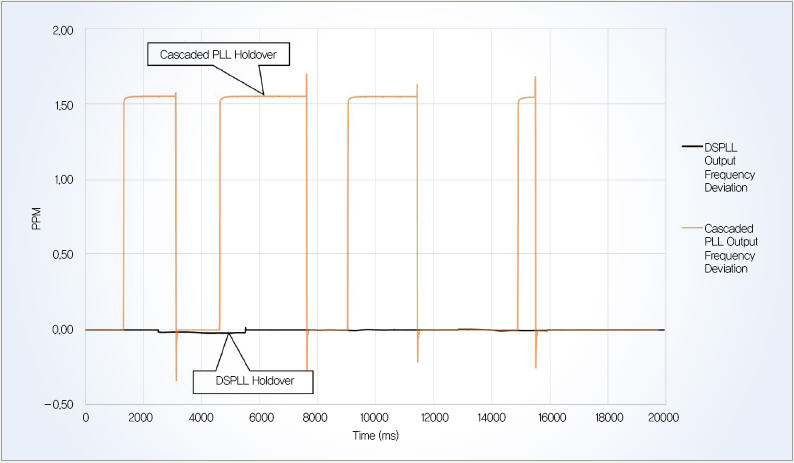

그림 9에서는 DSPLL과 캐시케이드 PLL의 홀드오버 성능을 비교해서 나타낸 것이다. DSPLL은 초기 주파수 오프셋 성능이 뛰어날 뿐만 아니라 홀드오버 애버리징까지 결합함으로써 홀드오버 애플리케이션으로 안정적인 성능을 달성한다.

▲ 그림 9. DSPLL은 매우 정확한 순간 홀드오버를 달성한다

진동의 영향

캐시케이드 PLL은 디스크리트 VCXO를 사용함으로써 진동에 훨씬 더 취약하다. 그림 10과 같이, 캐시케이드 PLL 평가 보드를 가볍게 두드리는 것만으로도 저주파 스퍼가 증가하고 잡음 플로어가 상승한다는 것을 알 수 있다.

▲ 그림 10. 캐시케이드 PLL은 진동에 취약하다

하지만 DSPLL 기술을 사용한 타이밍 디바이스의 경우, 같은 테스트를 실시했을 때 어떤 스퓨리어스 신호나 잡음 플로어 상승을 일으키지 않는다는 것을 알 수 있다(그림 11).

▲ 그림 11. DSPLL은 진동에 취약하지 않다

제임스 윌슨 _ 실리콘랩스