지난 호에서는 웨이퍼, 트랜지스터, 커패시터 및 메모리에 대해 알아봤다. 이번에는 최근 가장 핫한 이슈인 소형화와 관련해 동향을 짚어보고, 패키지 유형에 대해 알아본다.

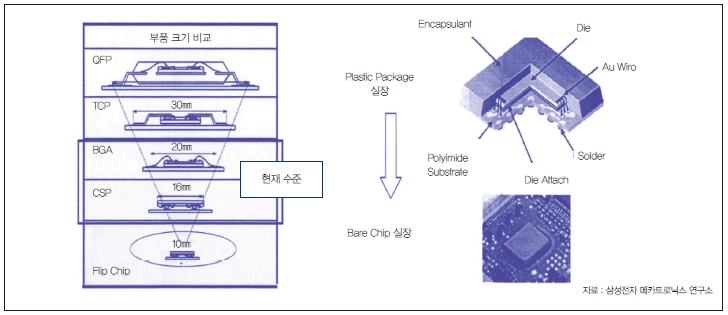

최근 C형 반도체 패키지의 소형화 및 Fine Pitch화가 빠르게 진행됨에 따라 플립칩이 도입됐다. 플립칩 실장 기술은 현재 사용되고 있는 QFP, TCP, BGA 등의 플라스틱 패키지 없이 반도체 칩을 뒤집어 보드에 직접 실장하는 것인데, 최근 이를 통해 실장면적 최소화 및 전기적 성능 향상을 도모하고 있다(그림 1).

그림 1. C형 반도체 패키지

하지만 플립칩 실장기술은 고 정밀도 실장이며 칩이 쉽게 깨지는 등의 문제점 때문에 SMT 대응에 해결과제가 있고 부품 단가도 높은 편이다.

이에 대응하기 위해 고밀도 SMT 기술을 확보하고 칩/기판/접속재료 등 최적화 설계를 위해 노력하고 있다.

다양한 패키지 종류 : BGA

BGA(Ball Grid Array)는 QFP의 다핀화·협 피치화의 진행에 의한 실장 곤란성을 해결하기 위해 개발됐다.

이는 이차원적 평면에 격자형식으로 분포된 솔더볼을 통해 패키지, PCB 등과 전기적, 기계적으로 연결하는 기술이며, 주변 실장 형태보다 단위 패키지 면적당 많은 I/O 수를 가질 수 있기 때문에 논리소자와 같은 고성능 패키지에 적합하다.

BGA의 장점으로는 솔더볼을 사용하기 때문에 전기적 접속에 유리하다는 점과 QFP보다 짧은 접속거리에 의해 낮은 인덕턴스와 커패시턴스를 갖는다는 점이다.

이 외에도 칩 바로 아래에 있는 솔더볼이 발생하는 열을 방출하는 역할을 하기 때문에 열 특성이 우수하고, QFP에 비해 적은 패키지 면적 및 비교적 넓은 피치, 그리고 솔더의 표면장력에 의한 Self-alignment 등에 의해 생산성이 높다.

하지만 솔더볼 연결 부위에서 응력이 발생해 접합부 신뢰성에 문제가 있고 접합부의 결함 검사 및 재작업이 어렵다.

주로 고기능 용도로서의 다핀화와 휴대기기 용도로서의 소형화에 사용된다.

1. P-BGA(Plastic BGA)

인터포저에 유기기판을 이용한 패키지로서 PCB 기판을 사용해 인덕턴스를 낮추고 전기적 열 방출 능력과 표면실장성을 대폭 향상시켰다.

또한 단자가 어레이형 형상으로 된 패키지 중 외부단자가 핀이 아닌 솔더볼로 구성돼 있으며, 2층 이상의 다층기판이 가능하다.

2. T-BGA(Tape BGA)

폴리이미드 테이프를 이용한 패키지로서, 회로 밀도 향상 및 기존회로보다 한층 더 강화된 내열성을 지녔다. 또한 폴리이미드를 기재로 사용한 2개의 메탈 필름 패키지로 설계됐으며, 1층과 2층 배선만 사용할 수 있다.

3. EBGA

기존 BGA에 비해 열적, 전기적 특성이 향상된 BGA로서, 표준계열인 PBGA(FBGA 포함)를 제외한 EPBGA, TBGA, VBGA 등이 이에 속한다.

일반적으로 캐비티가 아래로 향해 경제적이면서도 두께도 얇고 뛰어난 전기적 수행성능을 향상시킬 수 있는 패키지 유형이다.

4. HP BGA

HP BGA는 BGA 기술 중 딥 캐비티 다운(Deep Cavity Down) 방식으로 이루어져 있다. Ground와 신호를 위해 멀티 와이어 본딩을 이루고 있으며, 구리 열방출층으로 8∼10층을 이루고 있어 열적 성질이 매우 뛰어나 고전력용으로 응용할 수 있다. 이상적인 볼 피치는 1㎜이다.

5. MCM-PBGA

MCM-PBGA 기술은 고밀도 플라스틱 IC 패키징 중에서 가장 최근 기술이다.

고속 성능과 열적 우수성을 가진 Analog/Digital, Bipolar/CMOS, ASIC과 단일 IC 패키지 상의 DSP와 같은 Mixed 반도체 기술의 장점을 향상시키기 위한 발판을 마련했다는 평을 받는다.

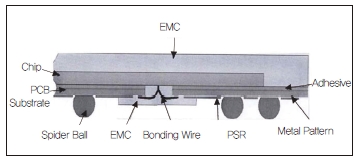

다양한 패키지 종류 : BOC

BOC(Board on Chip)는 CSP 중에서 DDR2에 사용되는 제품을 특정해 부르는 용어이다. D램을 패키징할 때 DDR-2부터는 리드 프레임이 아닌 BGA를 사용하는데, 일반적인 BGA의 구조와는 조금 다르게 칩이 거꾸로 실장되기 때문에 BOC란 이름이 생겼다.

DDR2는 칩의 I/O 부분이 일반적인 반도체와는 달리 칩 중앙에 배열되어 있기 때문에 와이어 본딩이 이루어지는 부분도 기판의 중앙에 위치한다.

DDR2에서 전통적인 메모리 모듈의 패키징 방식인 리드 타입을 사용하지 않고 BOC를 사용하는 것은 D램과 기판 간의 거리를 단축하여 신호 손실을 최소화하기 위해서이다. 이 점이 메모리 모듈에 대해서 모바일 기기와 같이 공간 제약성이 크게 나타나지 않음에도 불구하고 패키지 기판을 사용하는 이유이다. 클락 스피드가 기존 제품의 2배인 DDR2의 증가에 따른 신호 손실 최소화가 주된 사용 목적이다.

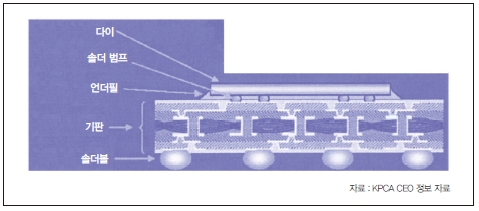

CPU 등의 속도 증가에 따라 메모리 속도도 증가하면서 기존의 리드 프레임 타입으로는 속도의 한계에 도달하게 되면서 IC기판에 형성된 슬랏(Slot)을 통해 다이의 본드 패드(Bond Pad)를 Au 와이어로 연결하고 다이는 IC 기판 상에 부착되어 있는 Adhesion을 통해 부착하기 때문에 전기적인 기능을 향상시킨 것으로 주로 DDR D램에 사용된다.

BOC의 기본 구조는 그림 2에 나타냈다.

그림 2. BOC의 구조

BOC가 생긴 유래를 보면 다음과 같다.

고속 시스템을 원하며 합리적인 가격의 수요에 대응하기 위해 데이터 비율을 두 배로 늘린 DDR(Double Data Rate)이 도입되면서 DDRAM용으로 사용할만한 TSOP를 대체할 수 있는 패키지 구조가 필요하게 됐다. 그 이유는 Micro BGA에서 논의한 바와 같이 Time Skew, Impedance Matching에 관한 것인데, Micro BGA를 거의 같은 성능을 유지하면서 좀 더 낮은 가격으로 하기 위해 노력한 결과 현재의 BOC구조가 탄생했다.

테이프 소재를 바꾸기 위해서 슬랏(Slot)이 뚫린 PCB로 소재를 바꾸고, 공정이 까다로운 리드 본딩 대신 패키지에 Au 와이어 본딩으로 대체하고 액상 에폭시 접착제와 Injection Mold 공정 등 범용의 CSP에서 많이 사용하는 공정을 도입하면서도 고성능 Micro BGA의 구조를 계승했다.

DDR은 시장에서의 성공과 함께 DDR2, 3을 거치며 전기적 특성을 개선하기 위해 2층 및 4층 기판을 채택하면서 최근 BOC까지 발전 했으며 현재 고속 메모리 패키지의 표준이 됐다.

다양한 패키지 종류 : COB

COB(Chip on Board)는 PCB 위에 다이(베어 칩)를 와이어 본딩해 연결한 후 몰딩하는 공정으로 이루어져 있다. 최근 베어칩 위에 또 하나의 베어칩을 마운트 한 상태에서 와이어 본딩하는 기술이 개발됐다.

다양한 패키지 종류 : CSP

CSP(Chip Scale Package)는 칩 크기에 가까운 소형 패키지를 총칭하는 것으로서, 외형에 리드가 돌출되어 있지 않은 베어칩에 가까운 크기의 패키지이다. 또한 칩의 면적이 패키지 면적의 80% 이상일 때 CSP라 한다.

CSP의 특징으로는 작고, 얇고, 가벼우며 Bare Ass'y 기술로 신뢰성과 작동성이 우수하다. 더불어 짧아진 리드와 리드의 인덕턴스 감소로 인해 SMT 패키지보다 향상된 전기적 성질을 갖는다.

이 외에도 BGA 기술보다 배선 밀도가 크며 실용적인 IC 패키징 프로세스와 물질을 사용한다는 점이 있다.

주로 휴대폰, PDA, 노트북 등에 사용되며 BGA 타입의 FBGA와 LGA 타입의 FLGA, 그리고 NON 리드 타입의 SON, QFN 등이 있다.

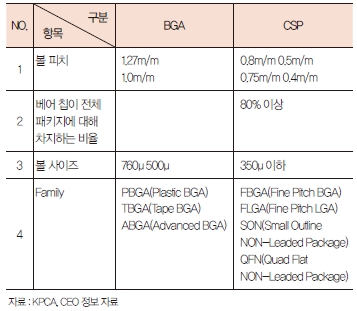

표 1에 BGA와 CSP의 차이점에 대해 나타냈다.

표 1. BGA와 CSP의 차이점

CSP는 비교적 비용이 저렴한 편이며 크기가 작을 뿐 아니라 성능까지 뛰어나기 때문에 인기가 많은 편이다. 또한 다이 표면을 보호하고 PCB와 다이 간에 발생하는 응력을 최소화하며, 다이와 PCB 간의 인터커넥트 배열을 손쉽게 변경할 수 있게 해준다.

특히 인터커넥트가 매우 짧게 유지되기 때문에 고속 신호 성능이 뛰어나다.

웨이퍼 제작, 다이싱 및 패키징으로 구성된 기존 프로세스와는 달리 WLCSP(Wafer Level Chip Scale Packaging)를 만드는 과정에서 전체 웨이퍼를 패키징한 후 이를 다이싱하기만 하면 된다.

하지만 CSP를 만들기 위해서는 패시베이션(Polyimide) 레이어로 웨이퍼를 덮은 후 비아를 본드 패드까지 에칭하고 비아를 전도성 소재로 채워야 한다. 그러면 구리 리트레이싱 레이어(Copper Retracing Layer)가 침전돼 비아의 맨 위에 연결되고 전체 칩에 매트릭스 패턴을 형성한다.

한편 PCB에 접촉되는 볼을 만드는 솔더 범핑 작업은 두꺼운 패시베이션 레이어를 침전하고 비아를 원하는 연결 지점으로 에칭한 후 솔더로 비아를 채우는 방식으로 이루어진다. 이후 패시베이션의 최상위 레이어가 제거되고 표면 장력으로 인해 솔더 열이 볼모양을 구성하게 된다.

지금부터 CSP의 유형에 대해 설명하려 한다.

1. FBGA

FBGA(Fine Pitch BGA)는 솔더볼 피치가 1㎜ 미만이며 외형 크기가 21×21mlm 이하인 소형 BGA이다. FBGA는 휴대폰 및 고밀도 실장을 목적으로 개발됐으며 인터포저로서의 유기기판, 세라믹 기판, 폴리이미드 테이프 등이 사용되며 칩과의 접속 방법으로는 와이어 본딩, TBA 접속, 플립칩 접속 등 다양한 구조가 있다.

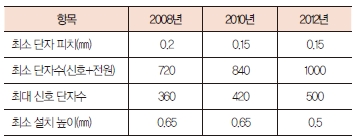

표 2에 현재 FBGA의 동향에 대해 나타냈다.

표 2. FBGA의 동향

2. FLGA

FLGA(Fine Land Grid Array Package)는 솔더볼을 형성하지 않고 금속 랜드를 접속용 전극으로 한 패키지이다. 랜드 피치가 1.0mlm 미만이며, 외형 크기는 21×21mlm 이하인 소형 LGA이다 인터포저로서는 유기기판, 세라믹 기판, 리드프레임이 사용되며 칩과의 접속 방법은 와이어 본딩 플립칩 접속이 사용된다.

표 3에 FLGA의 동향을 나타냈다.

표 3. FLGA의 동향

3. DDI

DDI(Display Drive IC)는 초박막액정 표시장치(TFT LCD)나 플라즈마 디스플레이 패널(PDP) 등 얇은 화면이 디스플레이도 작은 화소들이 수백만 개 이상 있다. 이러한 작은 점 같은 화소가 여러 빛을 발해 하나의 화면을 만드는데, 이를 조절하는 장치가 DDI이다.

다시 설명하자면, TFT LCD의 하나의 화소에는 빛의 3원색인 적, 녹, 청을 표시하는 부화소 3개가 있다. 이러한 부화소마다 하나의 트랜지스터가 설계돼 있고 이 부화소를 트랜지스터가 조종하는데, 이 트랜지스터를 조정하는 것이 DDI이다.

DDI에서 Gate IC는 명령을 내리는 반도체이며 Source IC는 조절하는 반도체 이다. 또한 TFT LCD나 PDP가 동작하기 위해서는 DDI가 반드시 필요하다. LDI(DDI LCD 구동칩)는 시스템 LSI 부분의 제품 중에서 삼성전자가 세계 1위를 기록하고 있다.

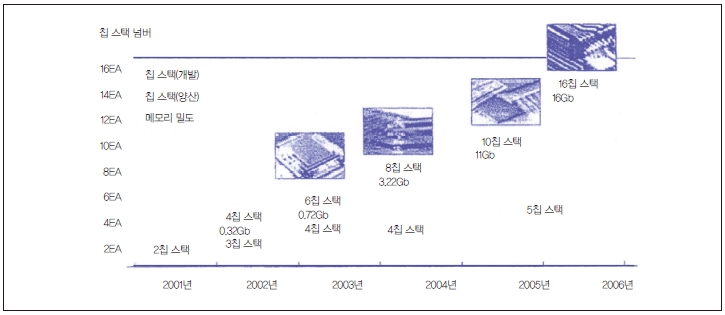

그림 3. 삼성전자의 MCP 발전 단계

다양한 패키지 종류 : MCP

MCP(Multi Chip Package)는 여러 개의 메모리칩을 쌓아올려 한 개의 패키지로 만드는 것으로써, 부피를 적게 차지하면서도 데이터 저장용량을 높일 수 있기 때문에 휴대전화와 같은 휴대형 전자 기기에 많이 사용된다.

최근 전자기기가 점차 소형화되면서도 필요로 하는 메모리의 종류와 용량이 늘어나면서 최소 부피에 최대한 많은 반도체를 쌓는 기술 개발이 가속화되고 있다.

이 기술은 휴대폰용 메인칩의 발전과 함께 해왔다. 휴대폰용 MCP의 경우에 8Mbit 플래시와 2Mbit S램과 같은 메모리 디바이스들을 하나의 패키지로 결합하면서 시작됐다고 볼 수 있다. 최근에는 휴대폰에 필요한 메모리 용량이 커지면서 NAND 플래시와 PS램(Pseudo SRAM) 등이 그 자리를 차지하고 있다.

그림 4에 삼성전자의 MCP 발전 단계에 대해 나타냈으며, 그림 5에는 삼성전자가 개발한 16단 MCP를 나타냈다.

그림 4. 삼성전자의 16층 MCP

그림 5. FC BGA의 구조

삼성전자는 지난 2003년에 6단, 2004년 8단, 그리고 2005년에 10단 MCP를 개발한 후 2006년에는 16단 MCP를 개발해 4년 연속 칩 적층 기술의 한계를 극복했다.

16층 MCP는 반도체 웨이퍼를 사람의 세포 크기(20∼30㎛) 만큼 얇게 가공한 것이다. 16단 MCP는 삼성의 8기가비트 낸드 플래시 16개를 쌓아 16기가바이트 낸드플래시 MCP가 된 것이다.

그렇다면, 왜 업계는 다층 MCP에 집착하는 것일까?

그 이유는 전통적으로 메모리반도체 기술력의 척도가 미세공정화였기 때문으로 보인다.

그도 그럴 것이 미세공정이 한 세대만 진화해도 같은 크기에서 D램의 경우 용량을 40% 이상, 낸드플래시의 경우는 80% 이상 늘릴 수 있기 때문이다.

이 외에도 메모리와 시스템반도체 등을 한 개의 패키지에 집적하는 복합칩이 대세로 부상하고 있다는 점도 간과할 수 없다. 결국 미세공정화 및 시스템온칩(SoC)화의 한계에 대한 보험으로 다층 MCP 기술 경쟁을 벌이고 있는 셈이다(표 4).

표 4. 주요 회사별 MCP 개발 현황

다양한 패키지 종류 : OCP

OCP(Open Cavity Package)는 개발 시 FIB(Focused Ion Beam) 분석 및 실리콘 디바이스 탐침을 수행하는데 적합하다.

이러한 테스트를 다이 위에서 하면 디자인 작업 속도를 높이고 대량 생산에 들어가기 전 디바이스의 무결성을 확보하는 데 많은 도움이 된다.

비교적 최근까지만 해도 이러한 디바이스는 대게 사이즈가 큰 세라믹 형태였다. 이들은 값이 비쌀 뿐만 아니라 패키지 인터커넥트가 최종 패키지에 사용되는 것과 같지 않기 때문에 고속 신호 무결성을 정확히 평가할 수 없다.

하지만 최근 이루어진 개발을 통해 이러한 모든 사항이 바뀌었다. 이제는 OCP를 QFN/MLP, QFP, SOIC/SSP 등의 여러 일반적인 포맷으로 사용할 수 있게 됐다.

한편 OCP와 같은 사전 몰딩 방식 패키지는 최신 JEDEC 아웃라인 및 풋프린트 표준을 준수한다.

패키지의 구리 리드 프레임은 군사 표준에 맞게 금으로 도금돼 있기 때문에 기계적인 안정성이 뛰어날 뿐만 아니라 대량 생산에 사용되는 완전 캡슐화된 형태의 몰딩 형태와도 전기적 특성이 매우 유사하다. OCP의 일반적인 패키지 크기는 3×3㎜에서 10×10㎜이다.

플립칩이란?

플립칩(Flip Chip)은 BGA처럼 패키지 타입을 일컫는 용어가 아니라 PCB나 리드프레임처럼 패키지 캐리어와 다이를 전기적으로 연결하는 방식을 뜻한다.

플립칩을 활용하면 반도체 크기를 대폭 줄이면서 전송속도는 기존 제품보다 20∼30배 빠른 기가급 이상을 낼 수 있으며, 선 없는 반도체로 불리기도 한다. 이 기술에는 반도체의 다리 역할을 하는 리드프레임이 없어 칩 사이즈가 곧 패키지 사이즈가 돼 세트의 소형 및 경량화에 유리하며, 칩 밑면에 입, 출력 단자가 있기 때문에 전송속도도 선이 있는 패키지보다 빠르다.

특히 기존 와이어 접촉법은 우수한 전기적 특성을 요구하는 대용량 D램, 속도가 빠른 S램, 고속으로 동작하는 마이크로프로세서 등에 적용이 어려웠던 데 반해, 플립칩은 이런 단점을 모두 보완해 1천 핀 이상의 입, 출력 단자를 갖는 반도체 칩에도 쉽게 적용할 수 있다.

FC(Flip Chip) 본딩이란 반도체 칩과 IC 기판을 전기적으로 연결하는 방법으로서, 반도체 칩의 전면이 IC기판을 향하도록 하고 반도체 칩과 IC 기판 표면에 형성된 수 십∼수 백 미크론 크기의 범프를 사용해 접속하는 것이다(그림 5).

플립칩 기술을 사용하면 다음과 같은 장점이 있다.

· 신호저항 계수 감소 : 다이와 캐리어의 거리가 짧아짐에 따라 신호저항 계수가 크게 감소하기 때문에 고속 통신과 스위칭 장치에 적합하다.

· 전기저항 계수 감소 : 와이어본딩의 경우, 다이 측면을 통해 신호가 이동하지만 플립칩은 다이의 면 방향으로 신호가 이동한다. 따라서 저항과 노이즈가 줄어든다.

· 높은 신호 집적 : 다이의 전체 면적을 접점으로 이용함에 따라 집적도를 높일 수 있다. 이는 QFP와 BGA 패키지를 비교하는 것과 유사하다.

· 다이 사이즈 감소 : 필요한 본드 패드의 수량과 면적에 의해 다이의 사이즈가 결정되던 이전의 방식을 벗어나, 다이 사이즈와 실리콘 비용을 줄일 수 있다.

· 패키지 풋프린트 감소 : 와이어본딩을 위한 공간을 줄이고 집적도 높은 기판을 사용함으로써 풋프린트가 감소 한다.

CSP는 접합 방식에서도 일반적인 패키지 접합과 차이가 있는데, 일반적인 패키지 접합은 솔더를 통해 이루어지지만 플립칩 패키지는 도체성질을 가진 접착제를 사용하는 Die 및 Carrier 접합 등의 두 가지 방식이 있다.

일반적으로는 솔더를 사용하지만 다이 표면에 형성된 도체 물질인 범프를 통해 접합한다.

지금까지 여러 패키지 종류와 CSP에 대해 알아봤다. 이를 토대로 현업에서 많은 도움이 됐으면 하는 마음을 담아 이번 호를 마치려 한다. 다음호에서는 PoP, QFN, QFP, SiP 등 나머지 패키지에 대해 소개하려 한다.

장동규 한국마이크로전자패키징연구조합