JESD204B 인터페이스는 언제 사용해야 할까?

설계를 전공한 사람이라면 누구나 JEDEC 표준에 대해 한번쯤은 들어봤을 것이다. 최근 JEDEC 표준을 나타내는 JESD204B 인터페이스에 대한 관심이 커지고 있다. 따라서 이 글에서는 JEDEC204B 표준의 발전 과정과 이런 인터페이스를 이용했을 때의 장점(빨라진 통신 속도, 간소화된 PCB 레이아웃, 작아진 패키지 크기, 원가 절감 등)에 대해 알아본다.

Sureena Gupta Shea 월드와이드 아날로그 마케팅, 텍사스 인스트루먼트

서론

FPGA를 사용하는 고속 데이터 수집(data capture) 설계를 전공한 사람이라면 누구나 JEDEC 표준을 나타내는 전문용어인 JESD204B에 대해 들어봤을 것이다.

최근 엔지니어들에게 많이 받는 질문 중 하나가 FPGA에서 JESD-204B 인터페이스가 어떻게 작용하는지, 좀 더 쉬운 설계를 하려면 어떻게 해야 하는지에 관한 것이다.

그렇다면 JESD204B 인터페이스란 무엇일까? 이 글에서는 JESD204B 표준의 발전과 이것이 시스템 설계 엔지니어에게 어떻게 사용되는지에 대해 살펴보고자 한다.

JESD204B 표준의 발전 과정

약 10년 전쯤 싱글 엔디드(Single-ended) CMOS 인터페이스가 차동 LVDS 인터페이스로 교체됐다. 그 이유는 후자의 데이터 속도가 더 빠르기 때문이었다(CMOS 인터페이스는 속도가 약 200Mbps로 제한되어 있다). 이뿐만 아니라 LVDS 인터페이스는 신호 라인과 전원 공급 장치의 잡음 커플링(Noise coupling)도 개선시켜 주었다. 하지만 이 인터페이스는 낮은 샘플링 속도에서 전력 소비가 높다는 단점이 있기 때문에 낮은 샘플링 속도가 적용될 때에는 여전히 CMOS 인터페이스를 사용하고 있다.

하지만 ADC(Analog-to-Digital Converters)가 진화하면서 더 빠른 샘플링 속도와 높은 채널 밀도를 요구하게 됐다. 따라서 업계에서는 병렬 LVDS 보다 더 빠르고 전력 효율적인 디지털 인터페이스에 대한 니즈가 늘어나게 됐다.

이를 해결하기 위해 JESD204라는 직렬 인터페이스가 개발됐고 2006년 4월 JEDEC의 승인을 받게 됐다.

JESD204 인터페이스는 최대 3.125Gbps의 통신 속도를 갖추고 있는 단일·복수 데이터 컨버터를 디지털 로직 디바이스와 연결하는 싱글 레인(single-lane) 고속 직렬 링크이며, 일반적으로 프레임을 동기화하기 위해 컨버터와 FPGA로 공통 프레임 클록을 전송해야 한다.

하지만 이를 사용하다 보니 한 개의 레인이나 직렬 링크만 지원하는 JESD204는 얼마 지나지 않아 생각보다 유용하지 않다는 것을 알게됐다. 그래서 2008년 4월 이 표준은 JESD-204A로 개정됐다. 이번 개정에서는 다중 정렬 레인과 멀티 포인트 링크에 대한 지원을 확장시킨 것이 요지였다.

하지만 이러한 개정에도 한계가 있었는데, 이는 최대 속도가 여전히 3.125Gbps로 제한되어 있었다는 것이다. 이에 여러 서로 다른 시스템 설계 과제를 처리할 수 있는 JESD204B가 2011년 7월에 개발됐다. 이 인터페이스는지원되는 데이터 속도가 3.125 Gbps에서 12.5Gbps로 크게 증가한 것 외에도 새롭게 추가된 확정적 레이턴스(deterministic latency) 기능을 사용해 멀티 채널 동기화를 크게 간소화시켰다.

JESD204B 표준이란?

JESD204B는 최대 12.5Gbps의 인터페이스 속도를 지원하고, 기존의 프레임 클록이 아닌 디바이스 클록을 사용한다. 또한 세 개의 서브클래스를 가지고 있다.

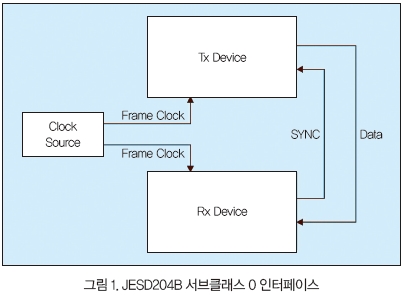

서브클래스 0은 속도가 빠르다는 점을 제외하고 JESD204A와 호환되며, 확정적 레이턴시를 지원하지 않는다. 또한 이 SYNC 신호는 오류 보고에 있어서 특별한 시간적 요건을 갖고 있다(그림 1).

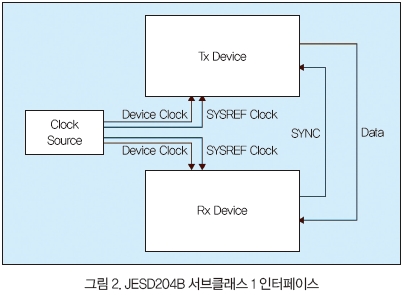

서브클래스 1은 동기화 신호인 SYSREF를 사용해 디바이스 전체에 걸쳐 로컬 멀티프레임 클록을 초기화하고 정렬한다(그림 2).

이를 통해 데이터 전송을 동기화하고 해당 디지털 링크를 거쳐 확정적 레이턴시를 달성할 수 있다.

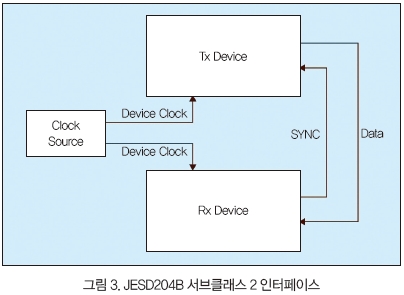

서브클래스 2도 같은 용도로 SYNC 신호를 이용하며,(그림 3) SYNC 타이밍 제약 때문에 400MSPS 보다 낮은 데이터 속도를 갖는 경우가 많다. 그래서 500MSPS 보다 높은 속도에서는 외부 SYSREF 클록을 사용하는 서브클래스 1을 더 선호한다.

JESD204B 호환 리시버는 Ser- Des(serializer/deserializer) 레인의 스큐(skew)를 보정하는 데 사용되는 탄성 버퍼가 구비되어 있어서 보드 레이아웃을 간소화할 수 있게 해준다.

이 탄성 버퍼는 가장 느린 레인의 버퍼가 도착할 때까지 데이터를 저장하는 역할을 한다. 이후 모든 레인의 데이터가 도착하면 동시에 방출해 디지털 프로세싱을 한다. 이러한 스큐 관리가 가능한 이유는 데이터 클록이 직렬 데이터 스트림(serial data stream) 안에 내재되어 있기 때문이다.

JESD204B 인터페이스의 기능 및 장점

JESD204B 호환 데이터 컨버터는 이전의 인터페이스보다 훨씬 더 빠른 속도로 데이터를 연속 전송하기 때문에 데이터 컨버터와 프로듀서 또는 FPGA에 필요한 핀의 수가 적고 패키지의 크기를 줄일 수 있을 뿐만 아니라 이로 인해 원가 절감까지 가능케 했다.

이 외에 핀 개수의 감소로 생기는 가장 큰 장점은 보드의 레인 수가 크게 줄어 PCB 레이아웃이 훨씬 단순해지고 루팅이 쉬워진다는 것이다.

스큐 관리의 필요성이 줄어든 덕에 레이아웃과 루팅은 한층 더 간소해질 수 있다. 이는 데이터 스트림에 내재되어 있는 데이터 클록과 리시버에 있는 탄성 버퍼 때문이다. 따라서 트레이스 스퀴글(trace suiggle)을 길이에 맞출 필요도 없다. 또한 JESD204B 표준은 더 긴 전송 거리를 보장한다. 완화된 스큐 조건으로 인해 로직 디바이스를 데이터 컨버터로부터 훨씬 더 멀리 배치할 수 있어 민감한 아날로그 부품에 영향을 미치지 않게 해준다.

더 나아가 JESD204B 인터페이스는 데이터 컨버터의 여러 해상도에 적응할 수 있다. 따라서 향후 ADC와 DAC를 위해 트랜시버/리시버(Tx/Rx) 보드를 물리적으로 다시 설계해야 할 필요도 없다.

LVDS 인터페이스의 전망

기존의 CMOS 인터페이스는 통신속도가 느린 데이터 컨버터의 전력 소비를 낮춰주는 반면 JESD204B 인터페이스는 LVDS 인터페이스보다 많은 장점이 있다. 그렇다면, 이 가운데서 LVDS 인터페이스가 살아남을 수 있을까?

간단히 대답하자면 ‘그렇다’고 할 수 있다. JESD204B 표준은 확정적 레이턴시를 사용해 멀티채널 동기화를 간소화할 수 있지만 애플리케이션들 중에는 최소의 레이턴시를 요구하는 애플리케이션도 있다.

이러한 애플리케이션(예, 레이더 같은 항공 우주 애플리케이션에는 어떤 행위나 감지에 즉각 반응해야 하기 때문에 지연을 최소화해야 한다. 따라서 이러한 애플리케이션에는 LVDS 인터페이스를 사용해야 한다.

그 이유는 JESD204B 호환 데이터 컨버터에서는 데이터 연속에서 지연이 생략되기 때문이다.

결론

이 글에서는 JEDEC204B 표준의 발전 과정과 이런 인터페이스를 이용했을 때의 장점(빨라진 통신 속도, 간소화된 PCB 레이아웃, 작아진 패키지 크기, 원가 절감 등)을 설명했다. 이를 통해 독자들이 JESD204B 기반 시스템을 이해하는 데 도움이 되었기를 바란다.