반도체 EMI/EMC 기술 및 표준화 워크숍

전자기 적합성 인증…‘무역 장벽’으로 작용

최근 시장에 출시되는 모든 전자기기는 시스템 레벨에서 EMI/EMC 특성을 모두 만족해야 하기 때문에 시스템 개발자는 EMI/EMC 특성이 좋은 부품을 사용하기 위해 부품 공급자로부터 납품 받는 부품과 더불어 EMI/EMC 인증서 및 그에 준하는 성적서를 요구하고 있다. 이에 맞춰 반도체 EMI/EMC 기술 및 표준화 워크숍에서 국내 EMI/EMC 분야 전문가들이 EMI/EMC 표준 문서 동향과 전자파 내성 향상 기술에 대해 발표했다.

임재덕 기자(smted@hellot.net)

한국표준협회(KSA)와 한국반도체산업협회(KSIA)가 공동 주최한 반도체 EMI/EMC 기술 및 표준화 워크숍이 지난 1월 16일 열렸다.

이날 행사는 국가기술표준원에서 추진하는 융복합반도체 분야의 ‘국가표준코디네이터사업’의 일환으로 개최됐으며, 국내 EMI/EMC 분야 전문가들이 연사로 참여해 EMI/EMC 표준화 현황과 기술개발에 대해 발표했다.

반도체 EMI/EMC 표준화 현황

1. 개요

과학기술이 발전하면서 생활 곳곳에서 전자파 발생량이 증가하고 있다. 따라서 전자기장해(EMI, Elecroma-gnetic Interference) 및 전자기 적합성(EMC, Electromagnetic Com-patibility)에 대해 알아보기 전에 전자파가 발생하는 원인부터 알아볼 필요가 있다.

전자파 발생 경로는 크게 의도적인 전파 발생과 비의도적인 전파 발생의 두 가지로 나눠 볼 수 있다.

- 의도적인 전파 발생원

· 방송이나 통신용 안테나(방송국 및 중계소, 기지국, 선박이나 항공 통신용 송신장치, 인공위성 등)

· 이동전화 단말기(휴대폰, Walkie-Talkie 등)

· 레이더, 온열 치료용 의료기기 등 다양한 주파수의 전파 발생원

- 비의도적인 전파 발생원

· 송전선, 가전기기, 산업용 전기장치, 의료기기, 컴퓨터, MP3Player 등

· 전기를 사용하는 다양한 종류의 기기

이처럼 전자파 발생이 늘어나면서 점차 EMI 및 EMC의 중요성이 대두되고 있다.

이는 과학기술이 발전하면서 점차 전자장치에 대한 높은 의존도, 무선통신의 광역화, 더 낮아진 구동 전력, 전자기기의 빠른 속도 등의 요인에 기인한 것이다.

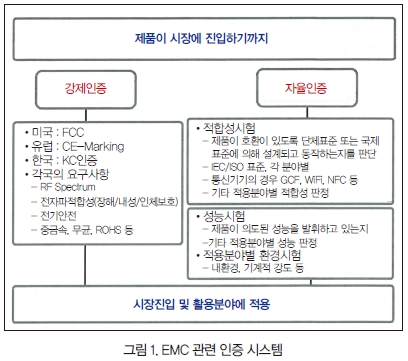

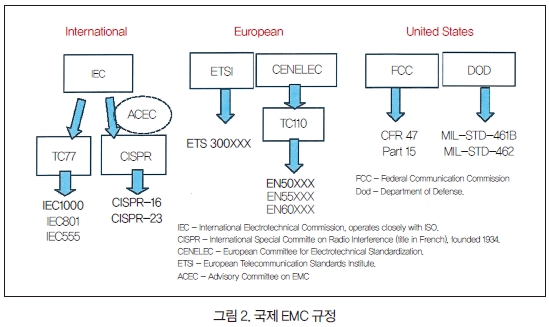

따라서 최근 많은 국가들이 수·출입 시 EMC 인증을 받지 못한 제품에 한해 세관을 통화시키지 않는 등 자체적인 무역장벽을 만들어내고 있다. EMC 관련 인증시스템에 대해 그림 1~그림 2에 나타냈다.

2. EMC 표준화 동향 : IEC TC 47

발표자 : 한국전자통신연구원, 김원종 박사

IEC TC 47은 반도체 소자에 대한 국제 표준화를 다루는 기술 위원회로서, 구성은 다음과 같다.

· SC 47A : 내부의 집적회로(IC)를 다룬다.

· SC 47D : 반도체 패키징을 다룬다.

· SC 47E : 개별 소자를 다룬다.

· SC 47F : MEMS를 다룬다.

이 중 SC 47A에는 다음과 같은 작업 그룹(WG, Working Group)이 있다.

· WG 2 : EMC 관련 시뮬레이션을 위한 집적회로 모델링

· WG 7 : 고급 하이브리드 집적회로

· WG 9 : 집적회로의 EMC를 위한 시험 절차 및 측정 방법

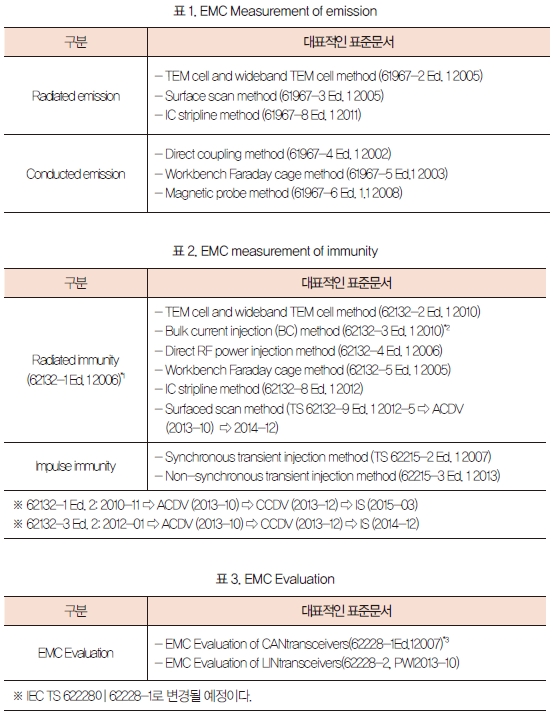

따라서 SC 47A에서는 WG 2와 WG 9를 중심으로 EMC 측정, 평가 및 집적회로 모델링에 대한 국제 표준 문서들을 발간한다. 관련된 대표적인 표준문서를 표 1~ 3에 정리했다.

3. 표준 분석 및 대응 : Electromagnetic Immunity

발표자 : KAIST, 김종훈 교수

현재 출시되고 있는 모든 전자기기는 시스템 레벨에서 EMI/EMC 특성을 모두 만족해야 하기 때문에 시스템 개발자는 EMI/EMC 인증서 및 그에 준하는 성적서를 요청하기 시작했다.

하지만 각각의 부품에 대해 어떻게 EMI/EMC 성적서를 만들어야 하는지에 관한 기준이 불명확하기 때문에 IEC SC 47A에서는 반도체 부품을 위한 EMI/EMC 특성 측정 방법을 제정하고 있다.

따라서 전자기 내성(Electro-magnetic Imm-unity) 측정 방법에 관한 규정인 IEC 62132 시리즈의 표준 문서를 분석해보고 적절한 대응 설계 기술에 관해 소개한다.

IEC 62132 시리즈는 집적회로의 전도성 및 복사성 전자기 내성 측정에 관하여 다루고 있으며, 다음과 같은 6개의 표준 문서를 포함하고 있다.

· IEC 62132-1 (General Conditio-ns and Definitions)

· IEC 62132-2 (Measurement of Radiated Immunity, TEM cell and wideband TEM cell Method)

· IEC 62132-3 (Bulk Current Injection (BCI) Method)

· IEC 62132-4 (Direct RF Power Injection (DPI) Method)

· IEC 62132-5 (Workbench Faraday Cage Method)

· IEC 62132-8 (Measurement of Radiated Immunity, IC Stripline Method)

따라서 이 문서들에 대해 간략히 설명하자면, 첫 번째로 IEC 62132-1 표준 문서는 집적회로의 전도성 및 복사성 전자기 내성 측정에 관한 일반적 정보와 용어 정의를 포함하고 있다. 이 문서의 주요 내용은 측정 시스템의 구성 중 DUT는 반도체 IC 칩 공급자게 의해 설계·제작되며 그 내용은 반드시 결과 보고서에 포함되어야 한다는 것이다.

두 번째로 IEC 62132-2 표준 문서는 TEM cell 혹은 GTEM cell을 이용해 복사성 전자기 내성을 측정하는 방법에 관한 규정이며, 반도체 IC 칩을 정상적으로 동작시킬 수 있는 DUT, 즉 EMC Test Board를 설계·제작하는 방법이 주요 내용이다.

세 번째로 IEC 62132-3은 Injec-tion Probe를 이용해 비접촉 방법으로 특정 도선 및 도선 그룹에 Common mode Current를 인가하는 BCI(Bulk Current Injection) 평가 방법, 즉 전도성 전자기 내성 측정에 관한 표준 문서이다.

이 문서의 주요 내용은 측정되어야 하는 Pin은 반도체 IC칩이 모듈 혹은 시스템에 실장 되었을 때, 외부로 연결되는 도선에 한하여 평가되어야 한다는 점이다.

다음으로 IEC 62132-4 표준 문서는 DPI(Diect RF Power Injection) 평가 방법에 대한 내용이며 IEC 62132-5 표준 문서는 WFC(Workbench Faraday Cage) 평가 방법에 대해 나타내고 있는데, 이 두 표준 문서 모두 IEC 62132-3 표준 문서와 상당히 유사한 점이 많다.

지금까지 전자기 내성에 관한 표준 문서를 살펴봤는데, 궁극적으로 전자기 내성을 강화하기 위해서는 Low Impedance Ground Path, on-chip 및 on-board Decoupling Capaci-tor, 수신회로의 S/N비 개선, Error Detection 및 Correction 회로를 채용하는 것이 도움이 된다.

반도체 EMI/EMC 기술 현황

1. 주기적 구조를 활용한 Crosstalk 감소와 신호 무결성 향상

발표자 : 서강대학교, 이행선 교수

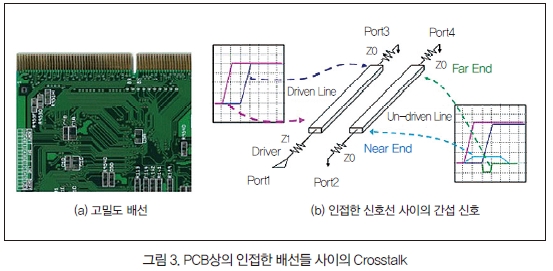

최근 부품들이 고집적화됨에 따라 개별 부품들의 입출력 신호를 연결해주는 PCB상의 라인 패턴들의 밀도 또한 높아졌다.

이에 따라 한정된 PCB기판 면적에서 높은 밀도의 배선을 형성하게 되면 신호선들 사이의 간격이 좁아지게 되고, 결국 인접 배선의 신호들이 서로 간섭하는 상황이 발생한다.

따라서 인접한 신호선의 전압 변화에 의해 의도하지 않은 간섭 신호가 전달되는 현상인 Crosstalk 문제가 발생하는데, 이 현상은 주로 신호선의 전압에 변동이 있을 때 심해지고 이때 전달된 간섭 신호로 인해 신호의 레벨을 바꿔 회로의 오작동을 낳는 주원인이 되고 있다(그림3).

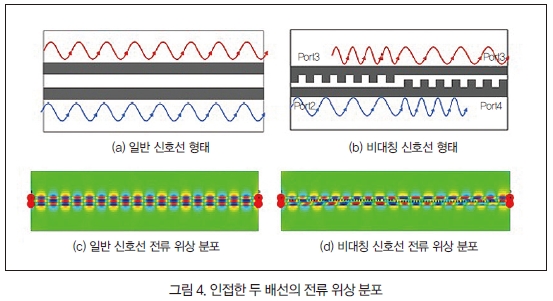

이러한 Crosstalk의 레벨을 낮추기 위해서는 인접한 배선 중 하나에 주기적인 스텁(stub)을 붙여서 비대칭 구조를 만들어야 한다. 비대칭 구조를 만들면 신호들의 진행 속도 또한 바뀌기 때문에 인접 신호들의 위상 차이로 인해 간섭이 줄어들게 된다.

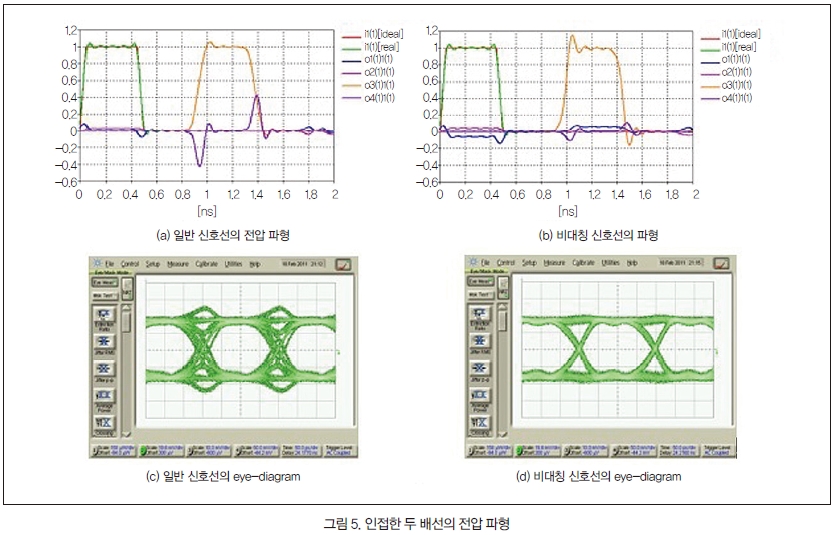

이를 설명하기 위해 그림 4에 일반적인 선로의 형태와 비대칭 형태의 선로에 대해 나타냈다.

비대칭 선로의 전기 신호 진행 속도가 달라졌는지 확인하기 위해 두 개의 선로에 동일한 사인파를 넣고 전류 위상을 시뮬레이션했다(그림 4(c), (d)).

그림 4를 보면 동일한 신호가 가해졌지만 비대칭 선로에서 전파 속도가 달라져 인접 신호선의 위상이 달라진 것을 볼 수 있는데, 이는 결과적으로 위상이 엇갈림으로 인해 간섭 신호들이 서로 상쇄되는 것이다.

또한 그림 5를 보면 일반 신호선과 비대칭 신호선의 포트 1에 사각형 펄스를 가했을 때 각 포트별로 출력되는 전압 파형을 확인해 볼 수 있다(실상황에서 주로 문제를 일으키는 포트 4의 전압이 Crosstalk에 의한 전압이다).

입력 신호로 1V를 인가했을 때 일반 신호선의 최대 전압이 0.4V이지만, 비대칭 선로의 Crosstalk는 0.1V정도 밖에 되지 않아 오작동 가능성을 낮출 수 있음을 알 수 있다.

그리고 그림 5 (c), (d)는 5GBps 펄스 신호에 대한 eye diagram 측정 결과를 나타낸다.

이 결과를 보면 비대칭 선로인 경우 상승·하강 지점이 Crosstalk의 감소로 깨끗한 것을 확인할 수 있다.

2. 저전력 시스템 반도체의 전자파내성 평가

발표자 : 성균관대학교, 김소영 교수

IT기기에 사용되는 반도체는 저전력 설계 요건을 만족시키기 위해 낮은 전원 전압을 사용한다.

하지만 낮은 전원 전압을 사용하면 회로가 견딜 수 있는 노이즈 마진이 급격히 감소해 외부 잡음에 취약하게 된다. 따라서 전자파 내성은 자동차용 반도체뿐만 아니라 IT 기기용 시스템이나 통신 반도체에서도 중요한 문제로 대두되고 있다.

IC 내부의 전자파 전도내성 평가는 주파수 별로 칩이 견딜 수 있는 주입 노이즈를 측정하여 이루어진다. 이런 평가를 진행함에 있어서 측정 시스템, PCB, 패키지 상에서 발생하는 손실을 고려해 회로의 취약점을 분석해야 한다. 따라서 전자파 내성을 개선하기 위해 IC 설계 단계에서 그 영향을 파악할 수 있는 시뮬레이션 툴이 개발되어야 하고, 이를 해결할 수 있는 회로 설계 방법도 지속적으로 개발 되어야한다.

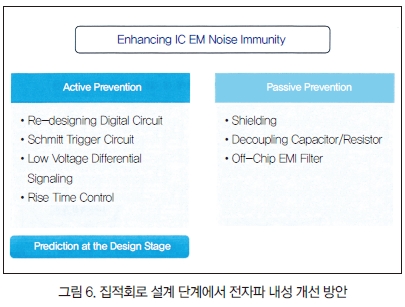

이에 대해 집적회로 설계 단계와 Digital 회로 설계 단계에서 내성을 개선하는 방법을 알아보면, 집적회로 설계 단계에서 전자파 내성 개선 방안은 다음과 같다(그림 6).

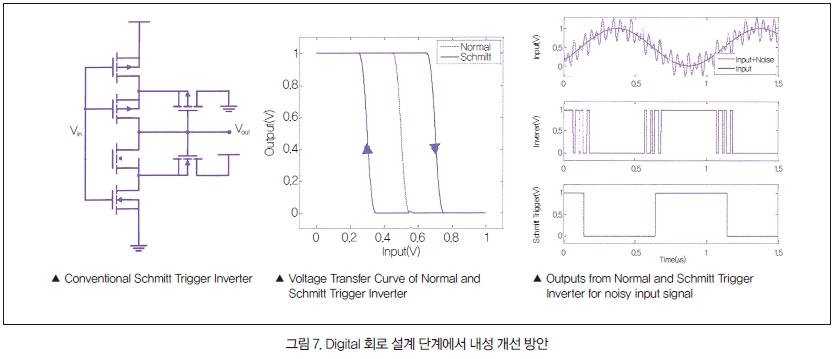

그리고 Digital 회로 설계 단계에서 내성을 개선하는 방법은 다음과 같다.

Hysteresis에 의해 L-H/H-L에 다른 threshold 적용 -> 면적이나 전력 소모가 증가하지만 전자파 내성이 개선됨(그림 7)

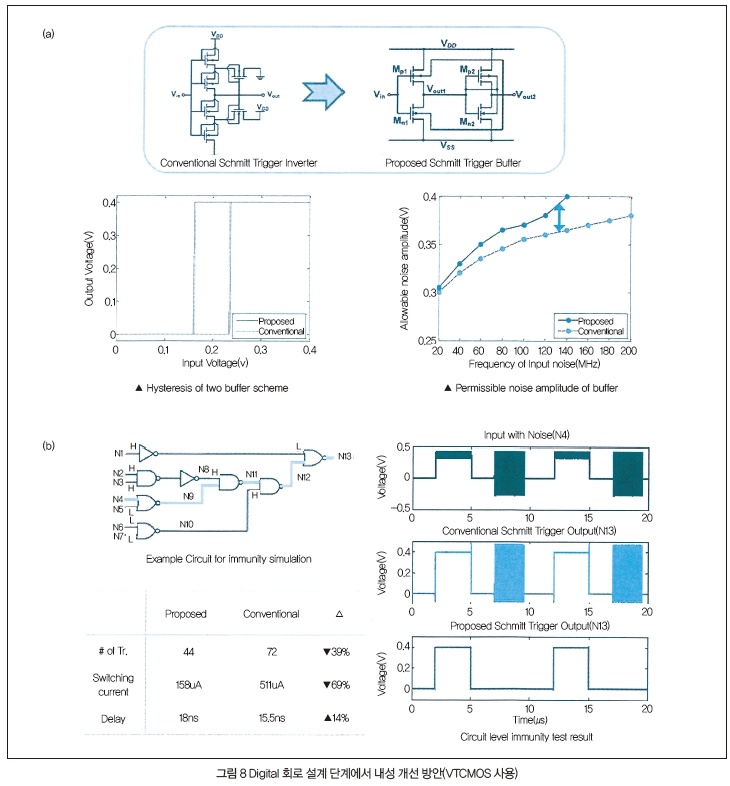

VTCMOS(Variable Threshold Voltage CMOS)를 사용하여 면적이나 전력 소모의 증가 없이 전자파 내성 개선(그림 8)

이처럼 앞으로도 많은 연구를 통해 내성을 개선하는 것이 중요할 것으로 보인다.