TSV 기술을 이용한 적층 패키지의 신뢰성 문제

TSV 기술은 기존의 와이어 본딩을 이용한 적층 기술에 비해 고성능, 저전력, 고집적화, 고기능의 장점을 제공하기 때문에, 최근 반도체 업계의 차세대 패키징 기술로서 개발이 한창 진행 중에 있다.이 기술을 특히 스마트 기기에 적용하면 배터리 전력 소모 문제 등을 어느 정도 해결할 수 있을 것으로 예상되는데, 이를 실현하기 위해서는 공정상에 여러 문제들과 패키지 비용 저가격화를 실현하는 문제를 해결하는 것이 요구된다. 여기서는 이 중 TSV 기술에서 중요시되고 있는 다양한 신뢰성 문제에 초점을 맞춰 살펴봤다.

TSV(Through Silicon Via)를 이용한 3차원 적층 칩 패키지 기술은 여러 개의 기판 혹은 다른 종류의 칩들을 수직 방향으로 적층(Stack)하는 형태의 패키징 기술이다.

일반적으로 이 기술은 실리콘 웨이퍼를 관통하는 미세 비아(via) 홀을 형성한 후 비아 홀 내부에 전도성 물질, 주로 구리(Copper)를 충전시켜 칩 내부에 직접 전기적 연결 통로를 확보하는 방식으로 적용된다.

이러한 TSV 기술을 사용할 경우, 기존의 와이어 본딩을 이용한 적층 기술에 비해 고성능, 저전력, 고집적화 및 고기능의 효과를 얻을 수 있기 때문에, 최근 이 기술은 반도체 업계의 차세대 패키징 기술로서 개발이 한창 진행 중에 있다.

특히 TSV 기술을 스마트 기기에 적용할 경우, 고질적인 문제로 지적돼 왔던 배터리의 전력 소모 문제를 어느 정도 해결할 수 있을 것으로 보인다.

때문에 향후 스마트폰 및 모바일 기기에 사용되는 반도체 칩은 대부분 TSV 기술을 이용한 칩 적층 방법이 사용될 것으로 예상된다.

그러나 아직 TSV 기술은 해결이 필요한 공정상에 여러 문제들과 패키지 비용 저가격화를 실현하는 문제가 남아있다. 이 중 특히 패키지 신뢰성에 대한 문제 해결이 향후 상업화에 도달하기 위한 큰 난제로 부각되고 있기 때문에 이 글에서는 TSV 기술의 다양한 신뢰성 문제를 자세히 살펴보고자 한다.

TSV를 이용한 적층 패키지의 신뢰성 문제

3차원 적층 칩은 다양한 재료를 이용하여 복잡한 구조로 형성된다. 이러한 구조에서는 배선(Interconnect)의 수가 증가하고 칩의 크기가 작아짐에 따라 열응력과 기계적 피로로 인한 파괴 등의 현상이 발생할 가능성이 높다.

특히 이 같은 오류 중 배선 간의 전기적 손실을 최소화하기 위한 재료로서 구리를 사용할 경우에 발생하는 신뢰성 문제에 업계의 관심이 커지고 있다.

구리는 실리콘 기판에 비하여 6∼7배의 높은 열팽창계수(Coefficient of Temperature Expansion, CTE) 값을 갖는다. 따라서 TSV 공정 중에 발생하는 열응력은 소자의 신뢰성에 커다란 영향을 미치는 것으로 확인됐다.

또한 비아 홀(Via Hole)의 직경이 작아짐에 따라 TSV에서 발생하는 응력 집중 현상 역시 간과할 수 없는데 이는 향후 낙하 충격 신뢰성 및 열 충격 신뢰성에 큰 영향을 미치는 요인으로 밝혀졌다. 현재 TSV 기술에 의해 발생할 수 있는 신뢰성 문제를 정리하면 다음과 같다.

·

열기계적 응력 및 파괴 현상

· 휨 현상(Warpage)

· 공정 및 웨이퍼 박형화에 의한 잔류 응력

· 솔더(Solder) 조인트 및 계면의 피로 파괴

· 적층 칩의 열 방출 문제

· 충격 및 기타 환경 신뢰성 문제

이 글에서는 앞에서 언급한 문제점들 중 몇 가지 중요한 이슈에 대한 개발 동향을 자세히 검토했다.

열기계적 응력 및 파괴 현상

앞에서 설명한 바와 같이 비아에 충진된 구리는 실리콘 기판에 비해 6∼7배의 높은 열팽창계수 값을 갖는다. 때문에 TSV 공정이나 신뢰성 시험의 열 사이클 응력(Thermal Cyclic Stress) 테스트에서 발생하는 열응력은 소자의 신뢰성에 큰 영향을 미칠 수 있다.

또한 실리콘 다이, 구리 비아 및 주변 물질들과의 열팽창계수 미스매치로 인해 발생한 열응력은 소자의 성능을 떨어뜨리는 것으로 나타났다.

예를 들면 100MPa의 응력 증가는 MOSFET 소자에서 약 7%의 캐리어 이동성(Carrier Mobility)을 감소시킨다고 발표된 바 있다. 이와 더불어 열응력은 실리콘 기판의 크랙을 발생시켜, 궁극적으로 소자의 파괴를 초래하는 것으로 확인됐다.

이러한 신뢰성 문제를 해결하기 위해 현재 다양한 방법과 연구들이 시도, 적용되고 있는데, 구체적으로 유한요소해석(Finite Element Method, FEM)을 이용하여 공정 중에 발생할 수 있는 응력에 대한 연구가 진행되었으며, 다양한 비아 형상에 따른 응력의 크기를 비교해 비아의 응력을 최적화하려는 노력이 시도됐다.

이와 관련해 Zhang 등1)은 구리 TSV 내에서 발생한 응력은 항복 응력(Yield Strength) 값 보다 클 수 있다고 보고했다. 또한 Lu 등2)은 구리 비아 부의 응력과 크랙(Crack)을 발생시킬 수 있는 응력강도(Stress Intensity) 값을 계산하여 구리 비아의 배치를 최적화하고자 했다.

그리고 Hsieh3)는 4층으로 적층된 패키지에서 유한 요소 해석을 통해, 열팽창계수 미스매치로 인한 열응력은 TSV와 실리콘 기판 사이에서 발생한다는 사실을 발표했으며, 이 경우 언더필(Underfill) 물질이 구리 비아 및 실리콘 다이(silicon die)에 미치는 영향을 민감도 해석을 통해 고찰했다.

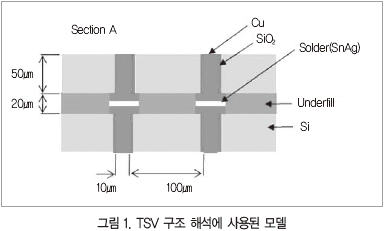

그림 1은 이 글의 해석에 사용된 TSV 구조의 개략도를 나타낸 것이다. 여기서는 이 모델을 바탕으로 해석을 수행했다.

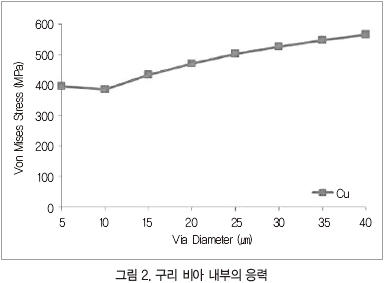

또한 그림 2는 비아의 직경이 10㎛, 피치가 50㎛일 때, 구리 비아를 중심으로 전체 패키지 단면의 본 미제스(Von Mises) 응력 분포를 보여준다. 관찰 결과 그림에 나타낸 바와 같이 비아의 크기가 증가할수록 구리 비아 내부의 응력은 증가하는 것으로 관측됐다.

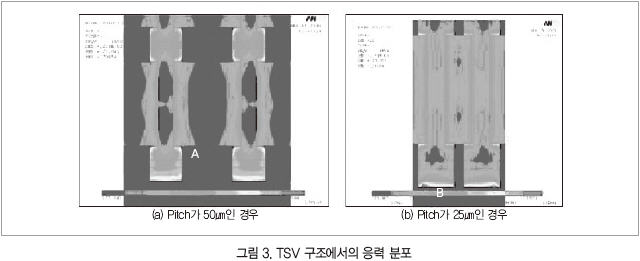

그림 3에서는 2개의 구리 비아가 존재할 경우의 응력 분포를 확인할 수 있다. 그림에서 응력은 A지점에서 최대가 되는 것으로 나타났는데 이 A지점은 구리 패드, 언더필 재료, 실리콘이 모두 맞닿는 계면으로, 이러한 계면 부분에 응력이 집중될 가능성이 크다.

그림3(b)은 비아의 지름이 10㎛, 피치가 25㎛일 때의 응력 분포를 나타낸 것이다. 그림을 통해 피치가 작아졌을 때, 즉 비아와 비아 사이의 간격이 25㎛로 매우 작아졌을 경우 비아의 응력이 다른 비아에 영향을 미쳐 비아 내부의 응력 및 주변 실리콘 칩의 응력이 증가하는 것을 알 수 있었다.

이처럼 비아 사이의 간격이 너무 작아지게 되면 비아와 비아 간의 응력 간섭이 발생해 비아 내부의 응력이 증가하게 된다.

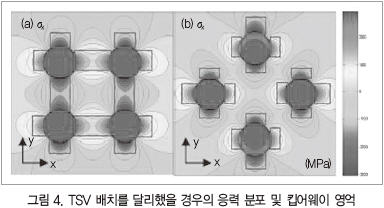

따라서 비아 간의 응력이 없는 상태를 추구해야 하는데 이러한 영역을 바로 킵어웨이 영역(Keep-away zone)이라고 부른다.

이러한 영역에서는 TFT나 소자가 위치하도록 설계해 소자의 성능이 저하되지 않도록 주의하는 것이 필요하다. Lu 등2)은 다양한 TSV의 어레이 형태에 따라 이 킵어웨이 영역이 어떻게 변하는지에 대한 연구를 수행했는데, 그림 4에 이 같은 영역의 일례를 나타낸다.

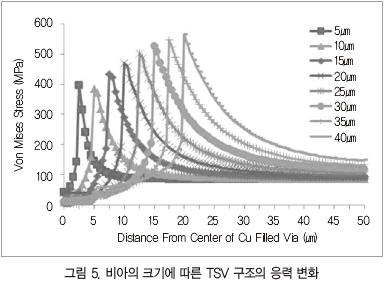

그림 5를 보면 비아 직경이 커질수록 비아 내부의 응력 및 주변에 미치는 응력에 대한 영향도 커짐을 알 수 있다. 이 경우 비아 내부의 응력은 비아의 중심에서 가장 적고, SiO2 층에서 가장 크게 측정됐다.

또한 비아의 직경이 40㎛인 경우에 비아의 최대 응력은 약 550MPa이 되는 반면, 실리콘 기판의 50㎛ 지점에서는 약 150MPa 이상의 응력이 나타나는 것으로 확인됐다.

비아 충진 재료의 영향

현재 비아를 충진하는 물질로는 구리, 텅스텐(W), 폴리실리콘이 보편적으로 사용되고 있다. 이 중 폴리실리콘은 매우 안정적이고, 다른 물질에 비하여 소자에 미치는 영향이 적기 때문에 그 사용량이 많은 편이다.

이와 더불어 텅스텐과 구리의 경우도 보다 낮은 저항 특성이 가능해지면서 최근에는 이 재료에 대한 수요가 크게 늘어나고 있다.

특히 TSV의 크기가 점점 작아지는 추세에 있기 때문에 텅스텐과 구리를 비아 충진 물질로 사용하는 것이 적극적으로 고려되고 있는데 이는 텅스텐이 실리콘과 유사한 열팽창계수를 갖으며, CMOS 공정에 적합한 특성을 갖고 있기 때문인 것으로 판단된다.

그러나 텅스텐은 매우 단단한 물질로 형성되므로 주변 회로 및 구조에 국부적인 응력이나 변형을 초래할 가능성이 많다. 더불어 구리의 경우는 열팽창계수가 실리콘에 비하여 4배 이상 크기 때문에 열팽창에 의한 신뢰성 문제를 초래할 수 있으며, 필요한 공정 또한 복잡한 것으로 알려져 있다.

따라서 공정을 단순화할 수 있고, 가격을 낮을 수 있으며, 동시에 신뢰성을 향상시킬 수 있는 비아의 충질 재료에 대한 개발이 중요시되고 있다.

이에 대응해 최근에는 니켈(Ni)을 3차원 DRAM 적층 기술에 적용하여 가격을 낮추는 방안이 제시되었다.

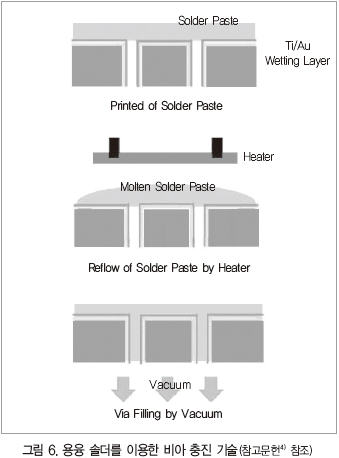

또한 한국생산기술원에서는 용융 솔더를 이용한 TSV 충진 기술을 개발했다.4) 이 기술은 그림 6에서 볼 수 있는 것처럼 용융솔더를 진공에서 사용하여 TSV를 채우는 방식으로 실현된다.

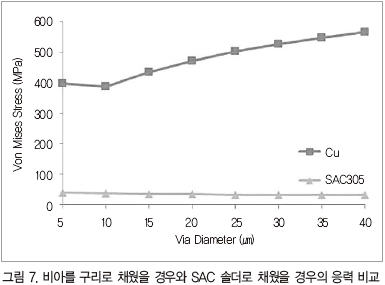

이 방법은 충진속도가 수초 정도로 매우 빠르기 때문에 생산성 면에서 획기적인 방식으로 평가되고 있으며, 특히 그림 7에 나타낸 바와 같이 솔더의 탄성계수가 매우 낮기 때문에 구리로 채웠을 경우와 비교했을 때 응력이 매우 낮은 장점을 제공하는 것으로 확인됐다.

공정 중에 발생한 휨 현상

최근 들어 TSV를 이용한 3차원 적층 패키지 기술의 가장 중요한 이슈 중 하나로, 본딩 얼라인먼트(Align- ment) 정밀도가 꼽히고 있다.

일반적으로 TSV 적층 공정은 얇게 박형화(Thinning)된 실리콘 칩을 본딩 기술을 이용해 고온에서 접합하는 적층 과정과, 칩과 칩 사이를 언더필 재질로 채우는 과정, 그 후에 어닐링(Anneal-ing)하는 과정을 반복적으로 수행해 구현된다. 즉 8층의 칩을 적층하려면 이러한 과정을 8번 반복해야 한다는 것을 의미한다.

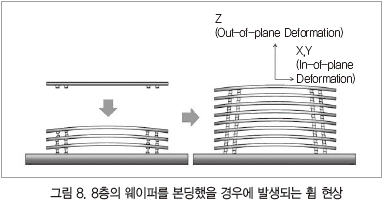

하지만 이처럼 고온과 상온의 공정 조건이 반복적으로 실행되면 실리콘 칩, 비아 홀에 충진된 구리 및 언더필 재료 등의 열팽창계수 차에 의해 휨 변형이 발생할 수 있다. 또한 이러한 휨 변형이 발생할 경우 적층된 칩들은 In-plane 및 Outof-plane 방향으로 변형될 가능성이 있다(그림 8).

그리고 이러한 변형은 칩을 접합하는 과정에서 본딩 얼라인먼트에 영향을 미치며, 종국에는 칩이 적층될 때마다 정렬 불량(Misalignment)의 양을 증가시킨다. 이 같은 문제를 해결하려면 본딩 공정을 할 때마다 실리콘 칩을 얼라인 혹은 정렬(align)하기 위하여 추가적인 공정을 실시하는 것이 필요하다.

통상적으로 이러한 얼라인 과정에는 광학시스템이 주로 적용되는데 실리콘은 투명하지 않기 때문에 광학시스템을 이용하여 적층된 상·하부의 칩을 동시에 정확하게 얼라인하는 것은 매우 어려운 과정에 속한다.

또한 정렬 불량의 양이 증가하면 비아 홀과 본딩 접합부 패드 사이의 접합 강도가 저하되거나 전기적인 손실이 발생할 가능성도 높아지게 된다. 즉, 휨 현상으로 인하여 적층된 칩들이 변형되면 본딩 접합부에는 전단응력이 발생하게 되고, 응력이 집중된 본딩 접합 면에는 파괴의 가능성이 증가하게 된다.

이러한 비아 홀과 접합부의 본딩 얼라인먼트의 양은 비아 홀의 크기와 직접적인 관계가 있다. 즉, 비아 홀의 지름이 작아지면 본딩 얼라인먼트에 요구되는 정밀도는 높아지게 된다.

예를 들면 ITRS 로드맵에 따르면 비아 홀의 지름은 2014년까지 5㎛ 이하로 작아질 것으로 전망되고 있는데, 여기에 적용 가능한 본딩 얼라인먼트 정밀도는 약 0.6㎛ 이하가 되어야 한다고 제시되고 있다.

한편 현재 TSV 기술에서 사용되는 본딩 기술은 매우 다양하다. 이 중 최근 들어 활발한 연구가 진행되고 있는 대표적인 본딩 기술로는 솔더를 이용한 Sn-Ag eutectic 솔더 본딩 기술, Cu-Cu 직접 본딩(Cu-Cu direct bonding) 기술, SiO2 직접 본딩(oxide direct bonding) 기술을 들 수 있다.

각 본딩 방법은 서로 상이한 장단점을 갖으며, 특히 본딩 온도가 각기 다른 특징을 갖는다.

먼저 Eutectic 솔더 본딩의 경우는 낮은 용융점의 솔더를 사용해 칩들을 저온에서 본딩시키는 방법이 적용되며, 금속간 화합물(Intermetallic Compo-und)을 형성하면서 본딩이 이루어진다.

그리고 Cu-Cu 본딩에서는 미리 뚫어 놓은 비아 홀에 구리를 채우고 구리 패드에 열과 압력을 가하는 열-압착 본딩(Thermo-compression Bonding) 방식이 기본적으로 적용되며, 이때 필요한 본딩 온도는 대략 350℃이다.

마지막으로 SiO2 직접 본딩의 경우에는 정밀하게 폴리싱(Polishing)된 실리콘 칩에 온도와 압력을 가하여 SiO2 산화막을 직접 접합하는 방법이 이용된다. 구체적으로 표면 세척 공정과 플라즈마(Plasma) 처리를 통해 표면을 친수성으로 만든 상태에서 고온의 열처리를 통해 본딩이 이뤄지며 이때 적용되는 본딩 온도는 300℃이다.

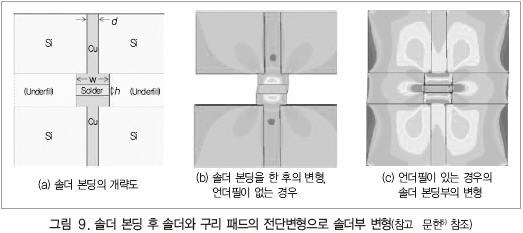

본 글에서는 우선 솔더 본딩과 관련해 본딩 공정 중에 발생하는 변형을 살펴보는 것을 목표로 했다. 이에 대한 예로서 그림 9를 관찰하면 솔더 본딩 후에 솔더와 구리 패드의 전단변형에 의하여 솔더부가 변형된 것을 알 수 있다. 이러한 변형이 발행하면 상부칩과 하부칩에 조정 불량이 발생하게 된다.

하지만 여기에 언더필을 사용할 경우, 언더필이 완충층(Buffer Layer)의 역할을 해, 약간의 응력 및 변형 감소 효과를 얻을 수 있다.

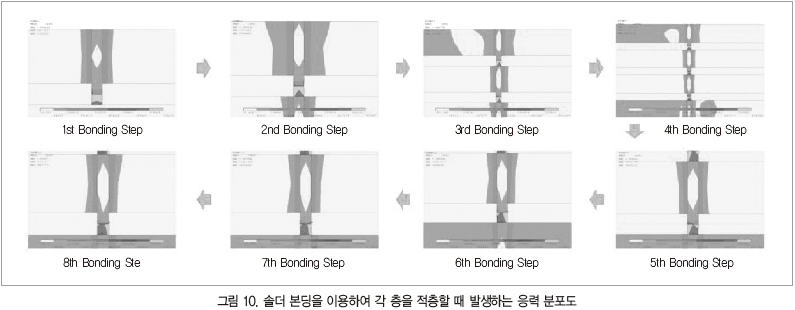

그림 10은 솔더 본딩을 이용해 실리콘 칩을 1층부터 8층까지 적층했을 때에 발생하는 TSV 구조의 응력 분포를 보여준다. 이때 나타난 응력분포를 보면 솔더와 구리가 접합되는 계면에 큰 응력 집중이 발생한 것을 관찰할 수 있다.

또한 비아 홀과 실리콘 칩 사이의 계면에도 응력이 집중된 것을 확인할 수 있는데 이처럼 솔더 볼과 구리 간의 강성과 열팽창 차이로 인하여 솔더볼과 구리 패드 계면에 큰 응력이 발생하면 균열 또는 파손이 생성될 우려가 있다.

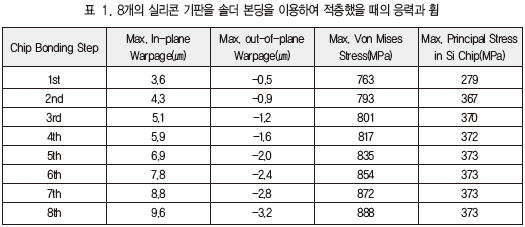

표 1은 8층까지 적층을 실시했을 때 발생한 휨 현상과 응력 크기를 나타낸 것이다. 이 경우 8층 칩이 적층되고 난 후에 발생된 휨의 양은 약 9.6㎛로, 비아의 직경이 10㎛임을 감안하면 비아의 직경만큼 조정 불량이 발생한 것으로 확인됐다. 이때 최대값으로는 373MPa까지 측정됐다.

이와 관련해 실리콘 재질의 파괴 응력이 1GPa인 점을 감안하면 실리콘 칩에서 응력에 의한 영향은 미미하다고 볼 수 있다. 그러나 실리콘은 취성 재질로서 여기서 발생하는 파괴 응력은 재료에 존재하는 결함이나 미세 손상에 의해 크게 좌우된다.

따라서 실리콘 칩의 파괴를 방지하기 위해서는 실리콘 기판 및 칩의 박형화 공정, 본딩 공정, 핸들링 과정, 즉 본딩, 디본딩(Debonding) 과정에서 칩이 손상이 되지 않도록 유의할 필요가 있다. 궁극적으로 본딩의 온도를 낮추는 것이 휨과 응력을 감소시키는 최선의 방법으로 판단된다.

결론

TSV 기술은 현재 개발이 한창 진행 중인 기술로서, 특히 시스템 반도체 분야에서 활용도가 매우 높은 기술이다. 그러나 아직 공정의 복잡성, 가격 문제, 신뢰성과 관련해 해결이 필요한 여러 가지 문제가 남아 있다.

이 글에서는 이에 대한 여러 가지 과제 중 다양한 신뢰성 문제에 초점을 맞춰 살펴봤는데, 향후에는 이 외에도 열방출 문제, 충격 낙하 신뢰성 문제들이 중요하게 다뤄질 것으로 예상된다.

그러나 TSV 기술이 갖는 많은 장점으로 인해 조만간 이 기술은 상용화에 성공할 것으로 판단되며, 이를 위해서는 기술 확보가 무엇보다 중요할 것으로 고려된다.

참 고 문 헌

1) Zhang. J. et al., "Modeling Thermal Stresses in 3-D IC Interwafer Interconnects", IEEE Tran. on Semicondutor Manufacturing, Vol. 19, No. 4, pp. 437-448, 2006.

2) Lu. K. et al., "Thermo-Mechanical Reliability of 3-D ICs containing Through Silicon Vias", 2009 Electronic Components and Technology Conference, pp.630-634, 2009.

3) Hsieh. M. C., Yu. C. K., "Thermo-mechanical Simulations For 4-Layer Stacked IC Packages," EuroSimE Conf., 1-7, 2008.

4) Ko, Y. et al. “High-speed TSV filling with molten solder”, Microelectronic Engineering, Vol 89, pp.62-64, 2012.

5) Shen, Y.-L. and Johnson R.W. “Misalignment induced shear deformation in 3D chip stacking: A parametric numerical assessment”, Microelectronics Reliability, in press

좌성훈 교수 서울과학기술대학교