[첨단 헬로티]

출력 전압을 빼내기 위해서는

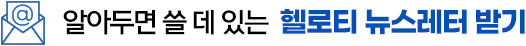

트랜지스터의 베이스에 신호 전압 vi를 가해주면 베이스 전류 ib가 흘러 큰 신호로 증폭된 컬렉터 전류 ic (= hfeib)를 얻을 수 있다. 여기서 이 증폭된 신호를 밖으로 빼내려면 부하 저항 RL을 컬렉터에 직렬로 넣어, 이 저항에 생기는 전압 vo을 취하면 된다. 즉 전류를 전압으로 바꿔내는 것이다.

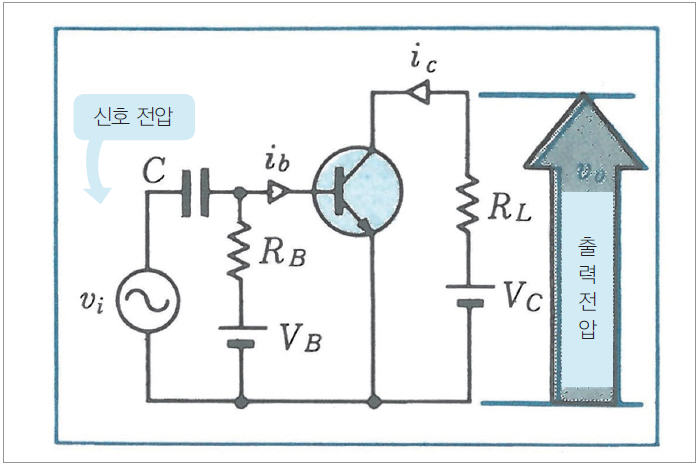

[그림 1]의 회로는 기본 증폭 회로라로 말할 수 있는데, 동작 원리에서 알 수 있듯이 트랜지스터 각 부의 파형은 직류분의 합으로 되어 있다. [그림 2]는 그 모양을 나타낸 것이다. 여기서 주의할 점은 컬렉터 전류 IC와 컬렉터 전압(출력 전압) vo의 파형은 위상이 반전된다는 점이다. 이런 것에 대해 생각해 보자.

▲ 그림 1. 신호 전압 vi와 출력 전압 vo 베이스 전류(입력 전압)

▲ 그림 2. 각부의 전압·전류 파형

IC와 vo는 왜 반전 되는가

우선, [그림 1]의 회로에서 직류분만을 주목한다면, 베이스측의 바이어스 전압 VB에 의해 컬렉터 측에 흐르는 전류 IC는 항상 일정한 크기의 전류가 흐르게 된다. 이 때 컬렉터 전압 vo는 직류 전류 IC에 의한 전압 강하 RL IC 에 따라 vo = vc - RLIC[V]의 크기로 된다.

그리고 [그림 3(a)]에 그 모양을 나타냈다. 신호 전압 vi가 가해지지 않으면 이 상태가 그대로 유지된다. 여기에 신호 전압(교류분)이 가해지면 컬렉터 전류 ic는 증감을 되풀이하게 돼 출력 전압 vo도 이에 따라 변화를 한다. 그런데 vo = vc - RLic라는 관계이므로, ic가 증가하면 RLic도 커지므로 따라서 vo는 작아진다. 역으로 ic가 감소하면 RLic도 작아지므로 역으로 vo는 커진다. 이 관계를 그래프로 나타내면 [그림 3(b)]와 같이 돼 ic와 vo는 역위상으로 된다.

▲ 그림 3. ic와 vo는 180° 위상이 엇갈린다

출력 전압 vo는 RLic로 생각해도 좋다

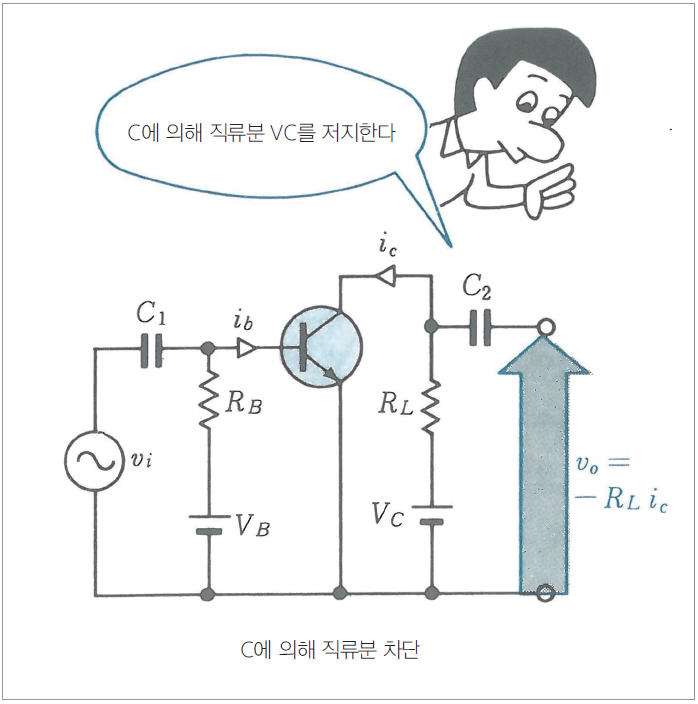

부하 저항 RL의 양단에는 RLIC라는 직류분에 대한 전압 강하와, RLic라는 교류분에 의한 전압 강하가 합쳐진 합성 전압이 걸린다. 그렇지만 [그림 3(a)]와 같이 직류분을 포함한 출력 파형이 외부에 흐르면 취급이 곤란하므로 [그림 4]처럼 직류를 저지하는 콘덴서 C2를 사용해 교루분만을 출력할 수 있게 한다. 그러므로 교류의 출력 전압만을 생각할 경우 vo=RLic로 된다. vo의 크기는 신호 전압 vi보다 커지기 때문에 전압 증폭이 가능하게 된다. 이 식에서 -부호는 입출력간의 위상이 반전된다는 의미를 가진다.

▲ 그림 4. C에 의하여 직류분 차단

트랜지스터 컬렉터 IC전류를 정하는 방법

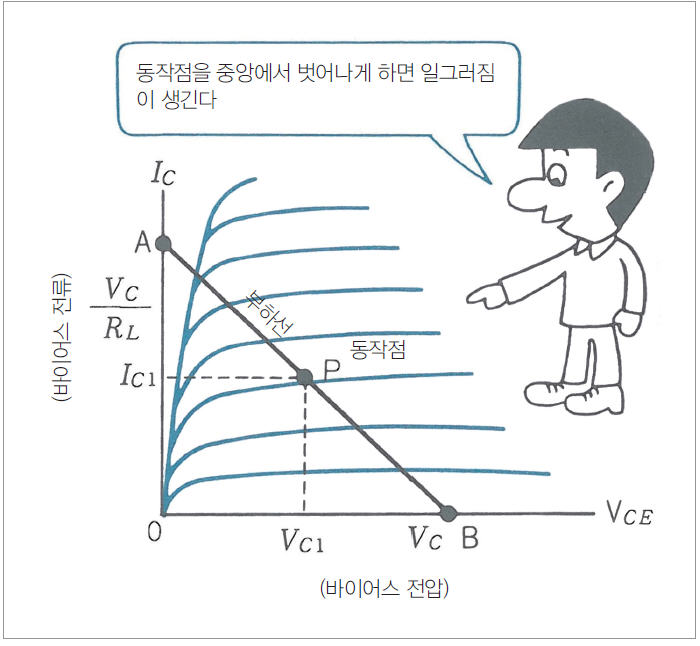

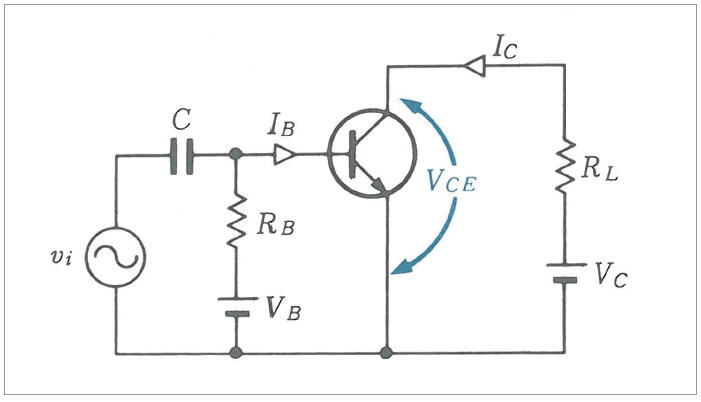

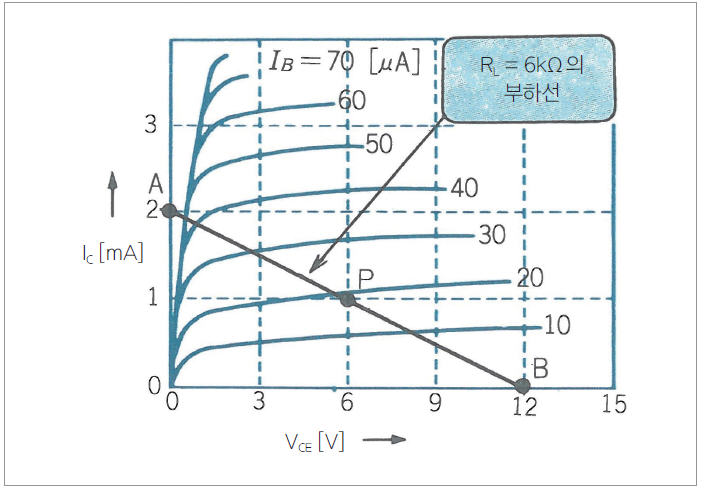

트랜지스터는 [그림 5]와 같은 VCE - IC 특성을 가지므로 이것을 이용해 컬렉터 전류 IC를 결정할 수 있다. [그림 6]의 증폭 회로에서 신호 전압이 0인 경우, IC = VC - RLIC의 관계가 있으므로 VCE와 IC의 관계를 VCE - IC 특성상에 그려 넣을 수 있다. 즉 A점과 B점을 구해 연결한 [그림 5]와 같은 직선이 된다.

▲ 그림 5. 부하선과 동작점

▲ 그림 6. 기본 증폭 회로

A점은 VCE = 0 경우로서, IC 축선상의 IC = VC / RL 값에 해당되는 위치가 된다. B점은 IC = 0인 경우이며, 따라서 VCE 축선상의 VCE = VC 값에 해당되는 위치다. 이 직선 AB는 VC와 부하 저항 RL을 트랜지스터에 접속함으로써 결정되는 것으로 부하선이라 부른다.

트랜지스터의 컬렉터 전압, 컬렌터 전류의 위치는 어느 경우나 이 직선상에 놓이게 되며, 이 부하선으로부터 입력 신호 파형에 대한 출력 전압이나 전류의 파형 또는 일그러짐 상태를 알아볼 수 있다. 입력 신호 vi를 가하지 않을 때에 직류 전압, 전류의 위치를 동작점이라 하며, 이것은 바이어스 전압을 결정하는데 있어서 매우 중요한 것이다. 일반적으로 [그림 5]에 나타낸 것처럼 큰 신호를 일그러지지 않게 증폭을 하려면 부하선의 거의 중앙을 동작점(P점)으로 잡는 것이 좋다.

계산하는 방법

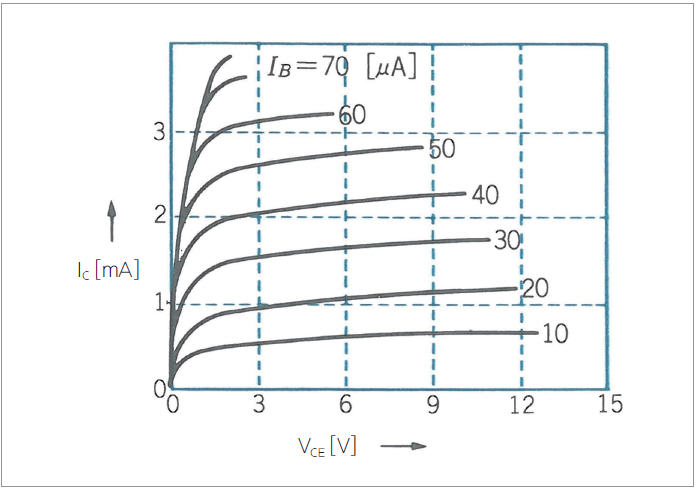

[그림 7]과 같은 VCE - IC 특성을 갖는 [그림 6]의 트랜지스터 증폭 회로에 있어서

▲ 그림 7. VCE – IC 특성

① VC = 12[V], RL = 6[kΩ]일 경우, 부하선을 그려라.

② 동작점 P를 부하선의 중앙에 잡으면 VCE, IC, IB는 각각 얼마나 되는가.

※ 풀이

① 부하선은 A점(IC = VC / RL = 12 / (6 × 103) = 2[mA])과 B점( VCE = VC = 12[V])을 연결해 [그림 8]과 같이 선을 그으면 된다.

② [그림 8]로부터 동작점 P의 위치는 VCE = 6[V], IC = 1[mA], IB = 20[μA]가 된다.

▲ 그림 8. RL = 6kΩ의 부하선과 동작점

신호 파형과 출력 파형

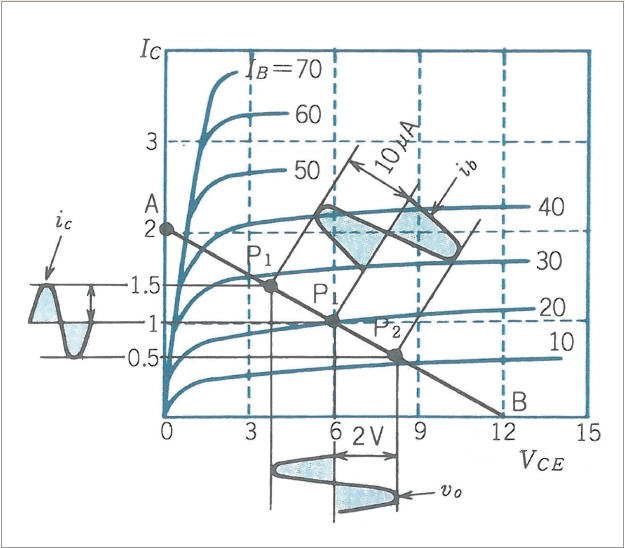

Q. [그림 8]의 부하선을 이용해 입력 신호 파형에 대한 출력 전압의 파형 변화를 알아보라.

A. 베이스 전류 ib가 20μA를 중심으로 ±10μA 변화할 경우, 컬렉터 전류 ic는 부하선상에서의 ±0.5μA변화를 한다. 따라서 출력 전압 vo의 변화를 그려보면 [그림 9]처럼 약 2V의 진폭이 되는 것을 알 수 있다. 실제로는 입력 신호 전압 vi의 진폭에 비해 대단히 큰 진폭인 것이다.

▲ 그림 9. 베이스 전류 ib의 변화에 대한 출력 전압 vo의 변화

전압, 전류, 전력의 증폭도

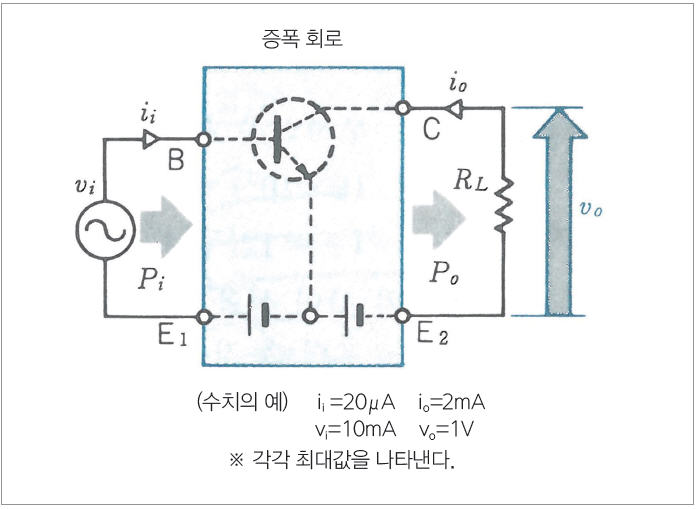

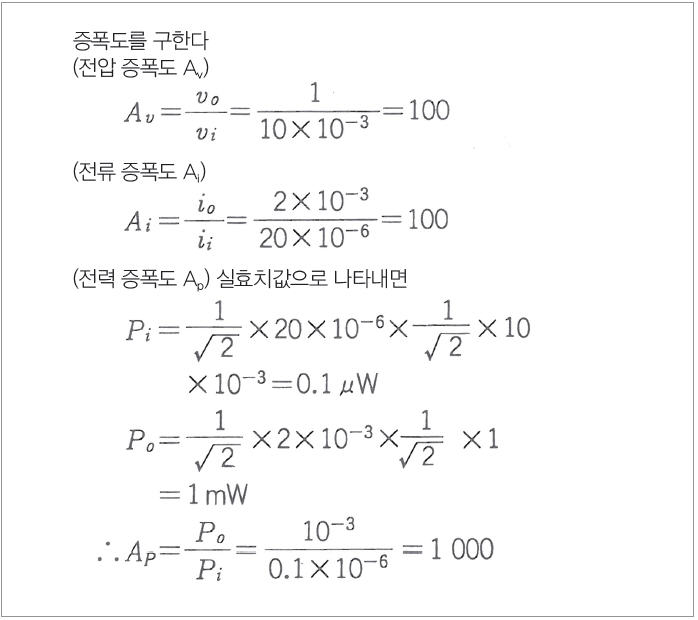

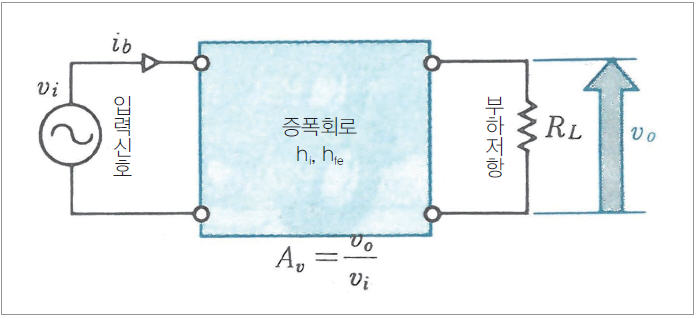

트랜지스터의 베이스에 입력 신호 전압 vi를 가했을 때, 컬렉터측 부하 저항 RL에 나타나는 출력 전압 vo를 얻을 수 있는 증폭 회로를 [그림 10]과 같이 표시해 놓았다. 일반적으로 증폭 회로는 [그림 10]과 같이 “입력과 출력을 가진 4각의 상자”로 봐도 무방하다. 여기서 출력 전압 vo와 입력 전압 vi의 크기비(최대값의 비) vo/vi를 전압 증폭도라 하며 AV로 나타낸다.

▲ 그림 10. 증폭 회로의 4단자 표시

또한 전류나 전력에 대해서도 똑같이 입력 전류 ii와 출력 전류 io의 크기비 io/ii를 전류 증폭도 Ai로 나타내고, 입력 전력 Pi와 출력 전력 Po의 크기비 Pi/Pi를 전력 증폭도라고 하고 Ap로 나타낸다. [그림 10]의 회로에 대한 수치를 예로 들어, 각 증폭도를 구해보면 [그림 11]과 같다. 계산의 예로 알 수 있듯이 전압이나 전류뿐만 아니라 큰 전류 증폭이 될 수 있다는 것이다.

▲ 그림 11. 증폭도 계산의 예

베이스 입력 저항이란

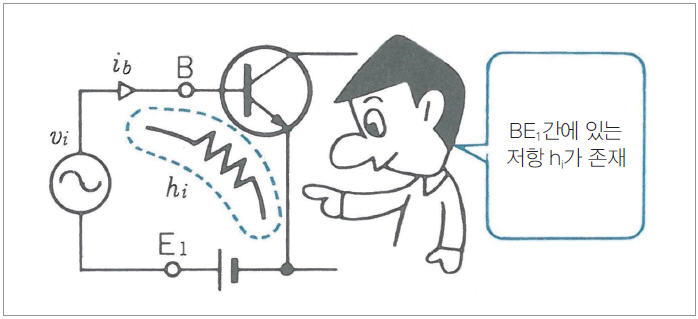

[그림 12]에서 vi에 의해 ib가 흐른다는 것으 B와 E1 사이에 “어떤 저항”이 존재한다는 의미를 가지므로, 이 저항을 hi로 나타내면 다음과 같은 식이 성립된다.

▲ 그림 12. hi = vi / ib

hi = vi / ib 또는 vi = hiib

이 hi를 이미터 접지에서의 베이스 입력 저항이라고 한다.

이미 출력 신호 전압 vo는 vo = RLic로 나타낸다는 것을 배웠다. 전압 증폭도 Av는 vo와 vi의 비이므로  로 된다. 그러나 ic / ib = hfe인 까닭에 Av = hfe(RL / hi)로 된다. 이 식은 전도를 구하는데 중요한 식 이다.

로 된다. 그러나 ic / ib = hfe인 까닭에 Av = hfe(RL / hi)로 된다. 이 식은 전도를 구하는데 중요한 식 이다.

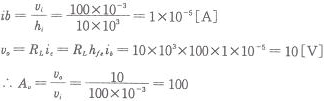

<문제> [그림 13]의 4단자 표시 회로에서 다음의 수치가 주어졌을 때, 전압 증폭도를 Av구하라.

hi=10[kΩ] hfe=100 RL=10[kΩ] vi=100[mV]

▲ 그림 13. 증폭도 A v의 계산

<풀이>

증폭도와 이해도의 관계

증폭도 회로의 증폭도를 나타내는데는 일반적으로 데시벨(dB)이라는 단위로 표시할 경우가 많다. 또한 전압, 전류, 전력의 각 증폭도를 데시벨로 표시한 것을 이득(gain)이라고 표현한다. 이들의 이득은 다음과 같다.

전압 이득 Gv =20log10Av[dB]

전류 이득 Gi =20log10Av[dB]

전력 이득 Gp =20log10Av[dB]

<계산 예> [그림 13]의 경우 Av = Ai = 100이고, Ap= 1000이므로

Gv = Gi =20log10100 = 20×2 = 40[dB]

Gp = 10log101000 = 20×3 = 30[dB]

* 전자기술이 반도체의 기초지식과 기술 이해를 돕기 위해 성안당의 <전자공학입문>을 연재합니다. <편집자 주>