결합 인덕터 SEPIC 컨버터의 장점

SEPIC은 종종 두 개의 자기 권선을 사용함으로써 식별된다. 이 권선은 결합된 이중-권선 인덕터와 같이 공통 코어에 감기거나, 결합되지 않은 인덕터 두 개의 별도 권선일 수 있다. 설계자는 어떤 기술이 가장 좋은지, 또 두 기술 사이에 실제 차이가 있는지 확신하지 못하는 경우가 있다. 여기서는 각 기술에 대해 살펴보고 실제로 SEPIC 설계에 미치는 영향에 대해 논의한다

John Betten, 텍사스 인스트루먼트 애플리케이션 엔지니어

회로 동작

싱글-엔드 1차-인덕터 컨버터(SEPIC : Single-Ended Primary-Inductor Coverter)는 정격 출력 전압보다 크거나 작은 입력 전압으로 작동할 수 있다. 벅(buck) 및 부스트 (boost) 컨버터로서 기능하는 것과는 별도로, SEPIC은 최소 능동 부품과 컨트롤러, 저잡음 동작을 제공하는 클램핑된 스 위칭 파형을 갖는다.

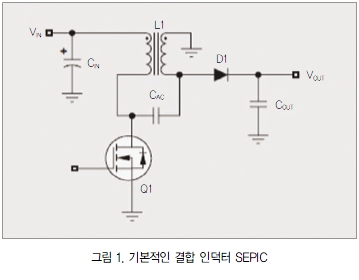

그림 1은 결합된 인덕터를 가진 기본 SEPIC을 나타낸 것이 다. FET(Q1)가 턴 온될 때 입력 전압이 1차 권선 양단에 인가 된다. 권선비가 1 : 1이므로, 2차 권선 또한 입력 전압과 같은 전압이 인가되지만, 권선의 극성으로 인해 정류기(D1)의 애노 드는 음극으로 가며 역-바이어스가 걸린다. 정류기가 바이어 스 오프되므로 출력 커패시터는 이러한 ON 시간에 부하를 지 원해야 하고, 이 시간은 AC 커패시터(CAC)가 입력 전압으로 충 전되도록 한다. Q1이 턴 온되는 동안 두 권선의 전류는 Q1을 거쳐 접지로 흐르며 2차 전류는 AC 커패시터를 거쳐 흐른다. ON 시간 동안의 총 FET 전류는 입력 전류와 출력 2차 전류의 합이다.

FET가 턴 오프될 때 권선의 전압은 전류의 흐름을 유지하 기 위해 극성이 반전된다. 2차 권선 전압은 정류기가 전류를 출력에 공급하도록 도통될 때 출력 전압으로 클램핑된다. 이 것은 변압기 동작을 통해 1차 권선 양단의 출력 전압을 클램핑 한다. FET의 드레인상 전압은 입력 전압+출력 전압으로 클 램핑된다.

두 권선의 FET OFF 시간 동안, 전류는 D1을 거쳐 출력으 로 흐르며 1차 전류는 AC 커패시터를 통해 흐른다.

V-㎲ 밸런스

회로는, 결합된 인덕터가 두 개의 결합되지 않은 인덕터로 대체될 때 유사하게 동작한다. 회로가 적절히 동작하려면 V- ㎲ 밸런스는 각각의 자기 코어 양단에서 유지돼야 한다. 즉, 두 개의 결합되지 않은 인덕터의 경우 각 인덕터의 전압과 시 간의 곱은 FET ON 및 OFF 시간 동안 크기가 같으며 극성이 정반대로 되어야 한다. 결합되지 않은 인덕터의 AC 커패시터 전압이 입력 전압으로 충전된다는 것을 대수적으로 나타낼 수 있다.

출력 측 인덕터는, 결합된 인덕터의 2차 권선이 그랬던 것처 럼, FET OFF 시간 동안 출력 전압으로 클램핑된다. FET ON 시간 동안, AC 커패시터는 인덕터 양단에 입력 전압과 같지만 극성은 정반대인 전위를 인가한다. V-㎲ 밸런싱은 각각의 간격 동안 인덕터 양단에서 클램핑되는 전압을 정의하여 듀티 사 이클(D)을결정한다.

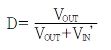

이것은, CCM(Continuous-Conduction-Mode) 동작의 경 우, 간단히 나타내면 다음과 같다.

이다.

입력-측 인덕터 양단에 인가한 전압은, FET가 온으로 될 때 입력 전압과 같다. FET가 오프일 때, V-㎲ 밸런스는 그 양 단의 VOUT을 클램핑함으로써 유지된다.

FET가 ON일 때, 입력 전압이 두 인덕터 양단에 인가된다 는 것과, FET가 OFF일 때 출력 전압이 두 인덕터 양단에 인 가된다는 것은 기억하기 쉽다.

결합되지 않은 인덕터 SEPIC 두 개의 전압 및 전류 파형은, 결합된 인덕터 버전의 전압 및 전류 파형과 구별하기 어려울 정도로 매우 유사하다.

2 대 1?

SEPIC 타입의 동작 회로에 차이점이 거의 없다면 어떤 것 을 사용해도 상관 없지 않을까?

결합된 인덕터가 두 개의 단일 인덕터를 사용하는 경우와 비교했을 때, 그 부품 수가 적고 집적도가 우수하며 인덕턴스 요건이 더 낮아 자주 선택된다.

그러나 더 높은 전력의 규격품인 결합된 인덕터는 제한적으 로 선택되므로 전원 설계자는 문제에 직변하게 된다. 그들이 만약 자신의 인덕터를 설계하기로 했다면, 더 오랜 리드 시간 을 처리해야 할 뿐만 아니라 모든 부속 전기 파라미터를 규정 해야 한다.

결합된 인덕터 SEPIC의 경우에는 누설 인덕턴스에서 장점 이 있을 수 있으며, 이러한 부분은 AC 전류 손실을 감소시킨 다. 결합된 인덕터는 V-㎲ 밸런스 때문에 1 : 1의 권선비를 가 져야 한다.

결합되지 않은 별도의 인덕터 두 개를 사용하도록 선택하 면, 통상 규격품인 부품을 더 넓은 범위에서 선택할 수 있다.

전류뿐만 아니라 각 인덕터에 대한 인덕턴스는 동일할 필요 가 없으므로, 다른 크기의 부품을 각각 선택할 수 있어, 더 큰 유연성을 제공할 수 있다.

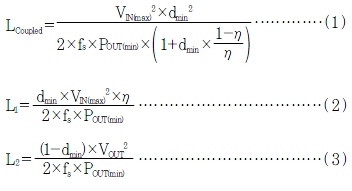

식 (1)∼식 (3)은 결합된 인덕터와 결합되지 않은 인덕터 모 두에 대한 인덕턴스 계산을 나타낸 것이다.

이 식은, 최대 입력 전압과 최소 부하에서 CCM 동작에 필 요한 최소 인덕턴스를 결정한다.

50% 듀티 사이클 동작(VIN이 VOUT과 같을 때 발생함)에서 이 들 식을 비교하면 식 (1)에서 결합된 인덕터에 대해 계산한 값 은 결합되지 않은 값의 두 배이다.

컨버터는 분명히 손실을 갖게 될 것이고 대부분의 입력 전 압원은 매우 가변적이므로, 이와 같이 간략화된 인덕턴스 생 성은 일반적으로 잘못됐다고 할 수 있지만, 극단적인 경우를 제외한 모든 경우에는 이것으로도 충분하다.

이 사실이 의미하는 것은 컨버터가 예상한 것보다 약간 더 빠르게(또는 더 느리게) DCM(Disontinuous-Conduction- Mode) 동작에 들어간다는 점이며, 이 부분은 대개의 경우 여 전히 허용 가능하다.

앞서 언급한 바와 같이 결합되지 않은 인덕터를 통해, 가정 한 바와 같이 출력-측 인덕터가 입력 측 인덕터와 같은 값일 필요는 없지만 이러한 가정은 간략화하기 위해 실행될 수 있 다. 출력 측 인덕터의 값은 입력 측 인덕터를 VOUT/VIN으로 조 정하여 간단히 결정할 수 있다. 더 낮은 값의 출력 측 인덕터 를 사용할 경우에는 통상적으로 더 작아지며 비용이 덜 든다 는 이점이 생긴다.

설계 예

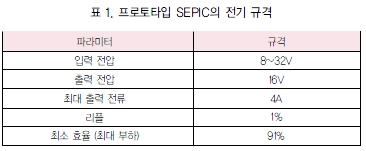

표 1에 나타난 규격은 설계를 비교하는 데 있어서 기초적인 것이다. 첫 번째 설계는 결합된 인덕터를 사용하고, 두 번째 설계는 두 개의 결합되지 않은 인덕터를 사용한다.

결합된 인덕터를 사용한 설계는 64W의 출력 전력을 가진 자동 입력-전압 범위를 대표한다.

식 (1)은 결합된 인덕터가 13A(IIN+IOUT)의 결합된 전류 정격 일 때, 12μH의 인덕턴스가 필요한지 결정한다. 이 설계는 규격 품 인덕터를 제한적으로 선택하기 때문에 특정한 어려움을 야 기시킨다. 그러므로 렌코 (Renco)社의 주문형 인덕 터를 규정하여 설계했다.

이 인덕터는 분리된 보 빈(bobbin)에 감겨 의도적 으로 누설 인덕턴스를 삽 입, 손실을 유도할 수 있는 AC 전류 순환을 최소화했 다. 이러한 손실은 누설 인 덕턴스 양단에 인가되는 AC 커패시터의 리플 전압 에 의한 것이다.

Coilcraft(MSS1278 시 리즈)와 Coiltronics (DRQ 74/127 시리즈)의 결합된 인덕터는 더 낮은 전력 설 계를 실현하는 데 우수한 규격품 대안을 제공한다.

결합되지 않은 인덕터 가 있는 설계의 경우 33μH Coilcraft SER2918이 L1 에 사 용 됐 고 , 22μH Coiltronics HC9가 L2에 사용됐다. 각각은 권선 저 항, 전류 정격 및 크기를 기초로 하여 선택됐다.

인덕터 선택 시, 설계자 는 코어 및 AC 권선 손실 도 주의해야 한다. 이러한 손실은 인덕터의 허용 가 능한 DC 전류를 감소시키 지만, 모든 벤더(Vendor) 가 이것을 계산하는 데 충분한 정보를 제공하지는 않고 있다. 이것을 적절히 계산하는데 실패하면, 통상적으로 40℃의 상승 을 초과하게 되므로 코어 온도를 상당히 증가시킨다. 이것은 또한 효율을 떨어뜨릴 수 있으며 고장을 앞당길 수 있다.

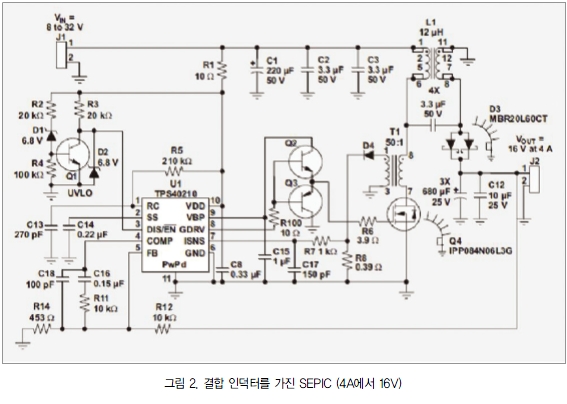

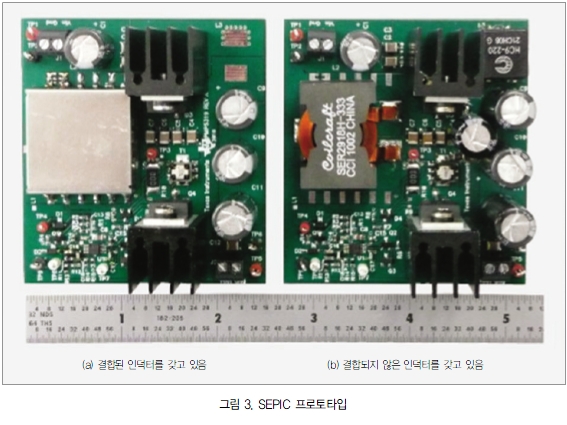

그림 2는 결합된 인덕터를 가진 프로토타입 SEPIC의 개략 도를 나타낸 것이다. 결합되지 않은 인덕터 설계로 구현하기 위해서, 결합된 인덕터는 동일한 PWB상에서 두 개의 인덕터 로 교체됐다.

그림 3은 두 프로토타입 회로를 나타낸 것이다. 그림 3(b)에 서 L1이 결합된 인덕터의 공간을 차지하며, L2가 상부 오른쪽 코너에 있다.

예상한 바와 같이, 두 회로는 거의 동일한 방식으로 동작했 으며 스위칭 전압과 전류 파형은 본질적으로 동일했다. 그러 나 성능 면에서는 몇 가지 핵심적인 차이가 있었다. 결합된 인 덕터 설계의 제어 루프는 상당히 양호했던 반면, 결합되지 않 은 인덕터를 가진 설계는 처음부터 불안정했다.

루프 게인 측정을 통해 높은 Q, 낮은 주파수 공진이 원인이 었다는 것을 결정했기 때문에 AC 커패시터와 병렬로 R/C 댐 핑 필터를 추가해야 했다.

공진 주파수는 아주 간략하게 나타낼 경우 대략적으로 다음과 같다.

SEPIC 회로는 상당히 복잡한 제어 루프 특징을 갖고 있으 므로 상세한 분석을 위해 수학 툴을 사용해야 하며, 이는 분석 결과를 종종 해석하기 어렵게 한다. 이 R/C 댐핑 필터(220μ F/2Ω)를 추가하면 비용, 회로 면적 및 손실이 늘어난다. 게다 가 하나의 결합된 인덕터에 비해 두 개의 결합되지 않은 인덕터에는 10%의 추가 면적이 필요하다.

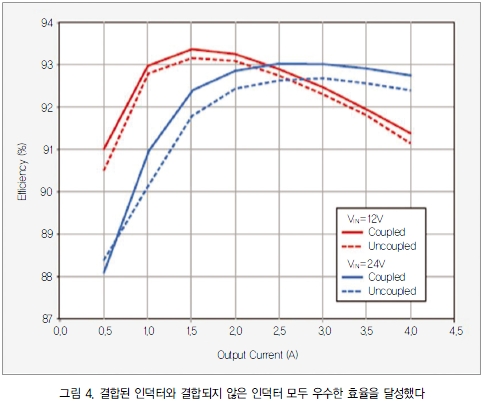

그림 4는 두 회로의 측정 효율을 나타 낸 것이다. 결합된 인덕터 설계의 경우, 보드 양단에서 최대 0.5%의 효율 상승이 있다는 것을 알 수 있다. 이것은 아마도 결합된 인덕터 설계 시 더 낮은 전체 코어 손실로 인한 것이며, 이렇게 손실이 낮은 이유는 그 DC 권선 손실이 결합되지 않 은 인덕터를 가진 설계의 손실보다 실제 로 더 높았기 때문이다.

L2는 분말-강철 코어 소재를 사용하며 이 소재는 L1 및 주문형 렌코 결합된 인덕 터에 사용된 강자성 소재보다 더 높은 손 실을 갖는 경향이 있다.(2)

L2에 대해 강자성 소재를 사용할 수도 있었지만, 그 경우 더 큰 면적이 필요해 졌을 것이다.

SEPIC은 결합된 인덕터나 두 개의 결합되지 않은 인덕터 중 어느 하나를 사용하여 성공적으로 구현할 수 있다. 개선된 효율, 감소한 회로 면적 및 양호한 제어 루프 특징은, 적절히 감긴 주문형 결합 인덕터를 사용할 경우 프로토타입 하드웨어 로 실현할 수 있는 장점이다. 주문형 부품이 규격 부품보다 덜 바람직할 수도 있지만, 결합된 인덕터의 경우 비록 크기가 더 작기는 해도 쉽게 이용할 수 있다. 출시 시간이 중요하다면 결 합되지 않은 인덕터가 설계자에게 더 큰 유연성을 제공할 것 이다.

[참고문헌]

1. John Betten. (May 27, 2010). SEPIC converter benefits from leakage inductance. PowerPulse.Net Design Features [Online]. http://www. powepulse.net/techPaper.php?paperID=153

2. Robert Kollman. (July 13, 2009). Power tip: Don’t get burned by inductor core losses. EE Times Power Management DesignLine [Online] http://www.eetimes.com/design/power-management-design/ 4012507/Power-Tip-Don-t-get-burned-by-inductorcore-losses