IBIS AMI vs. SPICE - 커뮤니케이션 시뮬레이션을 위한 최선의 선택은 무엇인가?

커뮤니케이션의 속도가 증가함에 따라 엔지니어들은 회로기판(PCB Assembly)이 만들어지기 전에 완벽하게 작동할 수 있도록 설계해야 하는 과제를 떠안게 되었다. 이러한 과제는 모델링을 통해 해결할 수 있지만, 매우 복잡한 작업이 될 수 있다.

커뮤니케이션 세계에서는 디바이스를 구동하는 채널의 행동을 모델링하기 위한 두 가지 솔루션이 경쟁을 벌이고 있다. 그 중 하나는 사실상 표준이라고 할 수 있으며 대부분의 시뮬레이터가 지원하고 있는 SPICE이고, 나머지 하나는 새로 등장한 제품으로 입출력에 대한 아날로그 모델링을 포함한 입출력 버퍼 정보 스펙(IBIS, Input-output Buffer Information Specification)의 확장판인 IBIS 알고리즘 모델 애플리케이션 프로그램 인터페이스 모델이다.

여기서는 이 두 가지 모델링 시스템의 기본적인 차이점을 검토하고, 고속 채널의 시뮬레이션과 관련된 각각의 주요 장점을 시스템적인 관점에서 살펴본다.

엔지니어들은 전자 산업 초기부터 수학을 사용하여 시간 영역과 주파수 영역 모두에서 회로의 동작을 계산했다. 여기에는 복잡한 계산이 요구되었으므로 오류가 빈번하게 발생했으며 많은 시간이 소요됐다.

현대적인 컴퓨터가 등장함에 따라 엔지니어들은 이러한 복잡한 계산을 처리하기 위해 소프트웨어를 개발하고, 인간이 만들어 낸 오차 성분을 제거하기 시작했다.

1960년대에 미국 국방부(DOD)는 회로의 방사선 손상을 시뮬레이션하기 위한 소프트웨어 개발 계약을 체결했다. 당시의 정치적 상황에 따라, 방사선이 배제된 비선형 회로에 대한 컴퓨터 분석(CANCER, Computer Analysis of Nonlinear Circuits, Excluding Radiation)과 같이 국방부가 개입하지 않은 시뮬레이터가 개발되었다. 이 컴퓨터 분석은 UC 버클리의 로날드 로러(Ronald Rohrer) 교수와 대학원생들에 의해 개발되었으며, 로렌스 나겔(Laurence Nagel)은 이 중 한 명이었다. 로러 교수의 성공으로, 나겔은 재산적 정보를 제거하고 새로운 시뮬레이터를 공공 영역에 출시하기 위해 CANCER 프로그램을 다시 쓰게 되었다.

SPICE의 탄생

1973년, 나겔은 한 학술회의에 SPICE(Simulation Program with Integrated Circuit Emphasis)를 발표했다. 하지만 SPICE가 갖고 있던 제한적인 요소 때문에 1975년 SPICE2가 출시될 때까지 널리 사용되지 못했다. 초기 버전은 포트란(FORTRAN)을 통해 제작됐다.

1983년에 되어서야 공대 학장인 아서 리차드 뉴튼(Arthur Richard Newton)의 지도로 토마스 퀄즈(Thomas Quarles)가 이 프로그램을 C언어로 다시 썼다. 새 버전은 이전 버전과 동일한 문법을 유지했으며 그래픽 X 윈도우 시스템에 대한 지원이 추가됐다. 이는 ‘오픈 소스’ 시뮬레이터로 공공 영역에 출시되어 SPICE 문법을 바탕으로 하는 다수의 상업 및 비상업적 시뮬레이터를 낳았다.

SPICE 시뮬레이션은 시뮬레이션되는 실제 회로를 나타내므로 재산적 정보를 포함할 수 있다. SPICE는 회로의 성능 시물레이션을 위한 완벽한 솔루션이지만, 회로에 설치된 트랜지스터의 수가 매우 많은 경우 계산 시간이 상당히 길어질 수 있다. 이는 특히 큰 비트 반복 길이(수백만 비트)를 포함할 만큼 오랫동안 시뮬레이션을 작동해야 하는 커뮤니케이션 채널의 BER(Bit-Error Rate)과 같은 시스템 특성을 모델링할 때 문제가 된다.

1980년대 초, 인텔에서는 재산적 정보를 노출하지 않으면서 보드 수준 시스템을 시뮬레이션하고, 시뮬레이션 시간을 줄이기 위한 수단으로 IBIS를 발전시켰다.

IBIS 모델링

IBIS 모델은 행동에 관한 것이다. 즉, 회로가 어떻게 실행되느냐를 드러내지 않고 버퍼의 아날로그 회로망의 행동을 정의한다. 이를 통해 제조업체 (집적 회로 및 전자설계 자동화 툴 제조사)와 시스템 엔지니어는 상호 연결의 아날로그 시뮬레이션을 위한 디지털 디바이스에서 사람이 읽을 수 있는 정보를 교환할 수 있게 되었다.

IBIS 모델은 I-V 테이블을 이용하여 버퍼의 출력 드라이브를 정의하고 V-t 테이블을 통해 출력의 변화율을 나타내며, 커패시턴스 정보를 활용하여 드라이버의 임피던스를 시뮬레이션한다. 온도, 전압, 공정 변화에 대한 정보가 제공된다면 버퍼의 행동을 매우 정확하게 시뮬레이션할 수 있다. 이러한 모델은 단순한 드라이버나 버퍼에서도 잘 작동하며 최상/일반/최악의 시나리오를 시뮬레이션할 수 있다. IBIS 모델에는 동시적 입출력 스위칭에 대한 시뮬레이션을 가능하게 하는 패키지 패러스틱 L과 C도 포함되어 있다.

그러나 버전 4까지 기본적인 IBIS 모델은 자가 조율 종료(Self-tuning Termination) 등의 복잡한 출력 행동을 지닌 진화된 드라이버의 경우 시뮬레이션할 수 없다. IBISv4.1과 4.2는 기능이 확장되어 핀 리스트, 패키지 정보, 시그널명 입력 한계점 및 출력 지연과 같은 IBIS의 장점은 모두 그대로 유지되고, 버퍼 선명도가 보다 개선된 아날로그(및 선택 형 디지털 HDL)로 교체되었다.

In IBISv5.0에서는 이러한 개념이 확대되어 AMI(Algorithmic Modeling Interface)를 포함하게 되었다. 이를 통해 이제 디엠퍼시스(de-emphasis) 또는 프리엠퍼시스(pre-emphasis)를 가진 드라이버와 채널 손실을 보상하기 위해 등화를 실행하는 리시버까지도 모델링할 수 있게 되었다.

확장 행동을 설명하는 API(App-lication Programming Interface)를 통해 모델에 DLL의 형식으로 컴파일 코드를 추가함으로써 이 작업을 수행할 수 있다.

현대적 버퍼 리피터, 리타이머(Re-timer), SerDes(Serializer/Deserializer)에서 찾아볼 수 있는 진화된 프로세싱이 더해지면서 복잡한 시스템에 대한 시그널 통합 시뮬레이션이 가능해졌다. 이러한 작업은 PCI Express와 10G 이더넷에서와 같이 속도가 보통 8Gbps를 넘어서는 경우 필수적이다.

IBIS AMI 모델은 임펄스 파형 시뮬레이션과 지속적 파형 시뮬레이션을 모두 제공하며, 함께 묶어 완전한 TX/RX(Transceiver/Reciever) 채널을 공급할 수 있다.

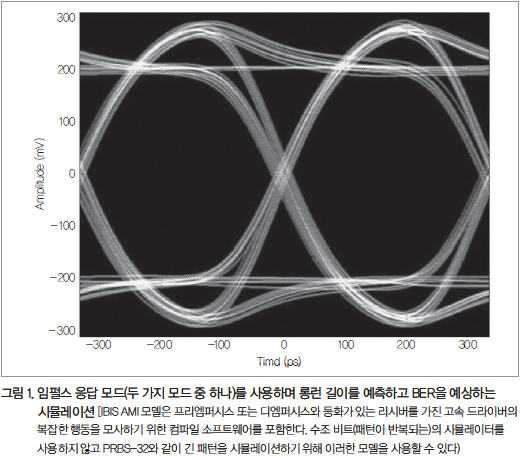

임펄스 응답 모드에서는 임펄스 데이터가 모델에 공급되며 모델은 프리엠퍼시스와 같은 프로세싱을 데이터에 적용하고, 그 후에는 수정된 데이터를 시뮬레이터에 돌려 보낸다. 데이터의 롱런을 통계적으로 시뮬레이션하고 아이패턴(Eye-pattern)이나 배스텁 곡선(Bathtub Curve)을 창출하며 BER 정보를 추론하기 위해 이러한 데이터를 사용할 수 있다. 동일한 프로세스가 모델에 대한 시간영역(Time-domain) 파형을 지나 데이터를 처리하고(등화 등) 시뮬레이터로 돌아가는 지속적인 시간 영역 모드에 적용된다. 이 방법을 통해 제조업체들은 실행 방식을 공개(SPICE의 딜레마) 하지 않고는 쉽게 모델링할 수 없는 복잡한 행동을 포함시킬 수 있게 되었다. 그림 1은 임펄스 응답 시뮬레이션의 일반적인 출력을 나타낸 것이다.

IBIS AMI의 모드는 고성능 채널 시뮬레이션 시 장단점을 모두 갖고 있다. 임펄스 모드에서는 임펄스 응답 데이터에서 직접적으로 결과가 계산되어 광범위한 통계적 범주를 검토할 수 있으므로 매우 빠른 모델링을 제공한다. 이것이 큰 실행 길이(Run Length. 예를 들면 2^32 비트)에 발생하는 문제를 연구하기 위한 방법을 제공하는데, 이러한 방법이 없다면 지속적인 파동 데이터를 시뮬레이션하는 것은 실용적이지 않을 것이다.

반면 지속적인 파형 데이터는 채널의 행동에 대해 보다 자세한 내용을 제공한다. 앞서 언급했듯이 IBIS 모델은 SPICE 모델과 비교했을 때 현격히 빠르므로 수백만 비트의 시뮬레이션을 실행할 수 있다. 그러나 시뮬레이션의 이와 같은 모드는 일반적으로 구체적인 패턴의 행동을 관찰하거나 이퀄라이저가 최적의 값에 도달하기 위해 필요로 하는 시간을 평가하기 위해 사용된다.

지금까지 매우 분명한 것처럼 생각될 수도 있겠지만, IBIS AMI와 SPICE 비교를 통해 본 바로는 최근 복잡한 고속 인터커넥트의 모델링에 있어서 IBIS AMI가 우세하다고 판단된다.

IBIS AMI는 인터페이스 구성 요소의 재산적 성질을 숨기고 임펄스 및 지속적 시간 작업 모드를 제공하며, 엄청나게 긴 시간 동안 시뮬레이션을 실행하지 않고도 디엠퍼시스, 등화, 클록 복구 등의 복잡한 기능을 시뮬레이션할 수 있도록 해준다.

채널 비트율이 10Gbps 이상으로 증가하면 시뮬레이션은 필수적이다. IBIS AMI 모델링을 통해 단일 트랜스미션을 구리로 에칭하기 전에 모든 복잡성에 대해 검토할 수 있다.

Rick Zarr 텍사스 인스트루먼트