지난 호에서는 OCP, PoP, QFN, QFP, SiP 등 다양한 패키지 종류와 SiC 기술의 동향에 대해 알아봤다. 이번에는 SiC와 Module Packaging 기술 등에 대해 알아본다.

SiC 공법…반도체 분야의 성장 견인

SiC(Silicon Carbide)는 반도체, 디스플레이, 조선, 화학 및 항공 등의 첨단산업에 반드시 필요한 소재로서, 내마모성, 열전도성, 강도, 인성, 내식성, 내화학성 및 내열성 등의 장점을 지녔다. 특히 반도체 분야에서 활용도가 높아 보인다.

주로 Dummy Wafer, Boat, Tube, Ring 등의 반도체 부품에 쓰이며, 최근에는 반도체 전 공정에서 실리콘이나 석영을 사용한 부품 대신 사용하는 추세이다. 또한 미국항공우주국(NASA)에서 우주선 터빈추진엔진 위치센서의 실리콘 칩을 SiP 칩으로 대체해 사용하고 있다.

고순도용 SiC(CVD-SiC)는 수입품이 대부분이며, 그 중 제조가 힘든 SiC 튜브나 SiC 보트 등은 프랑스의 생고방, 일본의 도시바와 아사히글라스 등이 과점하고 있다. 이는 다른 반도체용 제품 웨이퍼 캐리어 등에서도 비슷한 수준인 것으로 알려져 있다. SiC는 발광다이오드(LED) 태양전지 시장에서도 널리 활용된다. 반도체 시장과 거의 같은 규모로 사용되는 등 SiC 시장이 큰 성장을 보이고 있다.

1. SiC 제조 기술

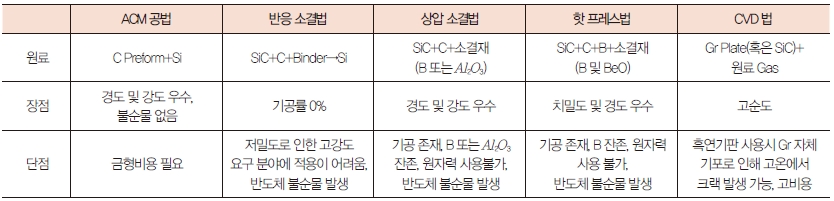

SiC를 만드는 기술은 반응소결법, 상압소결법, 핫 프레스(Hot Press)법, CVD 공법 등이 대표적이다. 이 공법들은 각기 다른 장점을 갖고 있지만 제조과정이 복잡하고 CVD 공법을 제외한 나머지 공법은 대부분 제품 생산과정에서 반도체 불순물을 발생시키는 단점이 있다.

만약 보론(B) 및 알루미늄(AI)과 같은 잔존물이 남아 있을 경우, 반도체 공정에서 파티클 소스로 나타날 수 있다. 이 경우 반도체 제조에 치명적인 결함요소로 작용하게 된다.

때문에 최대한 고순도 제품을 얻을 수 있는 방식이 필요한데, CVD 공법을 이용하면 반도체 불순물을 발생시키지 않고 고순도 제품을 얻을 수 있다. CVD 공정은 흑연에 SiC를 코팅하는 방식인데, CVD 공법도 최대 가능한 코팅 두께가 100∼200㎛에 불과하고 비용이 많이 들며 수명이 짧다는 한계가 있다.

최근에는 국내 한 벤처기업이 SiC를 만드는 기법중 하나인 ACM 공법을 개발해 기존 공정이 갖는 단점을 극복한 바 있다. 이 공법은 탄소로 성형한 프리폼과 금속, 비금속과의 반응 결합을 이용해 제품을 생산하는 것이다. 이 방식을 이용하면 기존 SiC 생산의 복잡한 과정을 생략할 수 있다.

또한 이론에 가까운 특성을 지닌 최대 두께 100㎜의 고밀도, 고순도 SiC 제조가 가능하며, CVD 공법에 비해 대형 사이즈 및 대량 생산에 용이하기 때문에 경쟁력이 있다.

더불어 기존 공법이 거쳐야 하는 복잡한 가공 과정을 간단한 후가공으로 대체할 수 있어 납기일 단축도 가능할 것으로 보인다. 표 1에 ACM, 반응 소결법, 상압 소결법, 핫 프레스법 및 CVD법을 비교했다.

표 1. SiC 공법 비교

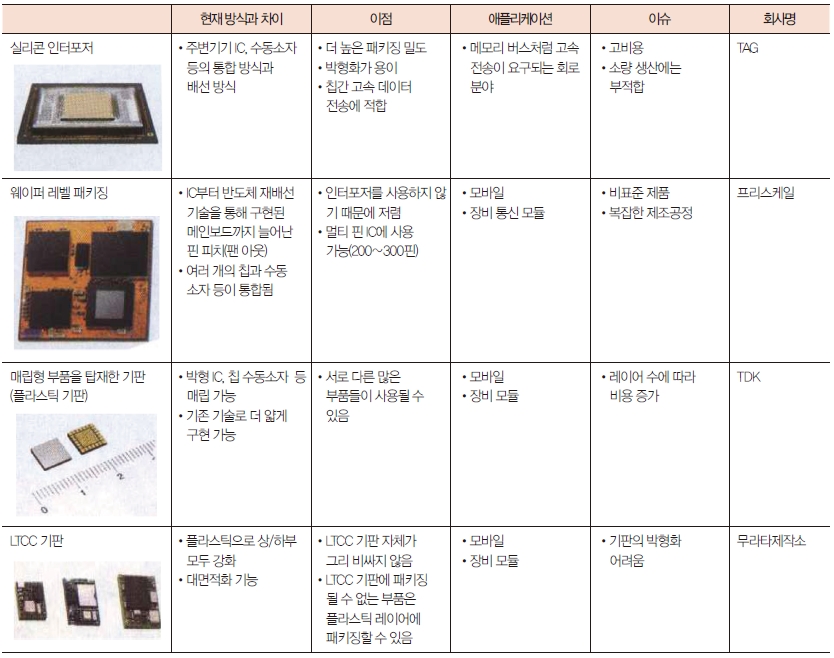

Module Packing 기술

이 기술은 개별 기판에 실장되는 여러 개의 부품을 소형 Single Package로 공급하기 위해 고안됐다. 또한 IC의 고속화 및 밀도 증가로 인해 모듈 기판 제작 요건이 까다로워지고 제작 원가도 치솟아 대응책으로 실리콘 인터포저, 웨이퍼레벨 CSP(WL-CSP) 등에 대한 새로운 모듈 패키징 기술이 등장했다. SiP와 RF 모듈 등의 솔루션은 다양한 형태로 전자 장비에 광범위하게 사용되고 있으며, 실리콘 인터포저, 웨이퍼 레벨 패키징, LTCC 등의 기술로 나누어 볼 수 있다.

1. 실리콘 인터포저

실리콘 인터포저(Si Interposer)는 실리콘 칩에 내장된 IC를 연결하기 위한 리드형이다. 초기에 ‘플라스틱 기판에 20/20㎛ 패턴을 제작하는 게 힘들다면 이미 검증된 기술을 사용해 배선 패턴을 실리콘 칩에 만들면 어떨까?’ 하는 발상에 착안해 제작된 회로 기판이다.

2. Wafer-Level Packaging WLP

웨이퍼 레벨 패키징 WLP는 IC 제조의 최종단계에서 실리콘 칩 및 부품 등을 서로 재연결 하는 것이다.

3. LTCC

LTCC(Low Temperature Co-Fired Ceramic)는 플라스틱 기판에 내장된 IC와 수동소자 및 기타 부품, 그리고 그 밖의 배선과 절연 등을 위해 서로 다른 레이어를 사용하며, 필름타입 수동소자가 내장된 LTCC 기판이 존재한다(표 2).

표 2. 모듈 패키징 기술 비교

멀티미디어 칩의 진화

1. 멀티미디어 칩의 발전과 휴대폰

국내 휴대폰용 멀티미디어 칩 설계 기업은 통신용 칩을 생산하는 거대 글로벌 기업과 휴대폰 제조업체 사이에서 멀티미디어 기능을 제공하는 반도체 설계를 통해 급성장할 수 있었다. 이들 기업의 성공기는 치열한 글로벌 IT시장에서 틈새시장을 공략, 국내 기술력을 메이저 수준으로 올려놓았다는 평가를 받고 있다. 또한 이들 기업의 멀티미디어 칩 기술은 현재 국내 휴대폰 산업 성장의 추진력으로 작용했으며, 이러한 점이 새로운 휴대폰 트렌드를 주도할 것으로 보인다.

과거 일반 전화가 ‘모빌리티(Mobility)'와 접목돼 ’휴대용 전화‘로 소개됐을 때에는 모바일 통신의 효율성이 강조되는 베이스밴드 칩의 발전이 중요했다. 또한 원거리에서도 자유롭게 통화할 수 있으며, 깨끗한 통화 음질을 제공하는 것이 중요했다.

본격적으로 휴대폰이 소비자의 곁으로 친숙하게 다가온 것은 휴대폰에 통신기능 외에 멀티미디어 기능이 접목되면서 부터이다.

특히 카메라가 장착된 핸드폰은 급속도로 소비자의 마음을 사로잡았다. 여기에 블로그 열풍이 크게 일어나면서 쉽게 휴대할 수 있는 대중적인 디지털 카메라에 대한 수요가 크게 늘었고, 이러한 복합적인 요소를 통해 카메라폰 시장이 급성장 할 수 있었다.

결국 카메라폰의 기술 성장은 SoC 시장에 새로 진입하려던 국내 팹리스 기업들의 성장에 풍요로운 토양이 됐다.

즉, 휴대폰에서 카메라 기능을 구현하는 CAP(Camera Application Processor)를 개발하면서 카메라 이외의 기능들을 탑재하는 MAP를 기반으로 한 멀티미디어 칩의 시대를 맞이하게 된다.

2. MAP 개발과 팹리스 산업의 발전

휴대폰 제조업체들은 급변하는 소비자의 요구에 부응하는 다양한 기능의 휴대폰 제조를 서둘렀으며, 이러한 추세에 힘입어 디지털 카메라뿐만 아니라 MP3, 모바일 TV, 모바일 게임, 텔레뱅킹 등 다양한 기능을 강조한 피쳐폰을 만날 수 있게 됐다.

또한 카메라폰용칩(CAP)을 개발한 이후에는 다양한 멀티미디어 기능을 탑재할 수 있는 기술력을 확보한 국내 팹리스 기업들은 멀티미디어폰용칩 개발을 통해 피쳐폰 시대에 대응했다.

팹리스 업체는 이후 MAP 개발을 통해 MP3 기능이 탑재된 뮤직폰, DMB 구동이 가능한 DMB 폰, 게임을 즐기는 소비자들을 위한 모바일 게임 폰 및 거리와 위치를 확인할 수 있는 GPS 폰 등을 출시했으며, 지속적인 발전 결과 모바일 환경에서 즐기는 멀티미디어 시대가 눈앞에 펼쳐지게 됐다.

45㎚ 반도체 공정…저전력화 실현

인텔은 45㎚ 수준의 반도체 공정 기술을 주도하며 저전력화를 실현했다. 배선폭을 45㎚로 줄이면서 1과0의 신호를 처리하는 스위치 역할 트랜지스터의 크기가 줄어듦과 동시에 스위치를 켜고 끄는 데 드는 에너지를 30% 이상 줄일 수 있게 됐다.

인텔이 선보인 바 있는 모바일 펜린 프로세서에는 ‘딥파워 다운’ 기술이라는 전력 관리 모드를 탑재했다. 이는 프로세서가 작동하지 않는 동안 전력 소모를 현저히 줄여 트랜지스터 내부 전류 유출 문제를 해결하며, 노트북의 배터리 수명 연장에도 도움이 된다.

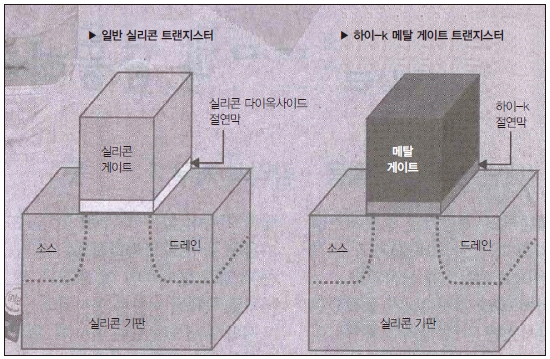

회로 선폭이 줄면서 생기는 전력 누설 문제는 신소재 개발을 통해 해결했다. 인텔의 45㎚ 공정에는 전류가 흐르는 채널과 트랜지스터를 분리시켜 주는 게이트 절연체로 새로운 하이-k 및 메탈 게이트 물질이 사용됐다. 기존 실리콘 다이옥사이드 대신 하프늄 기반 물질을 적용해 전력 유출을 크게 줄인 것이다.

이에 그림 1에 일반 실리콘 트랜지스터와 하이-k 메탈 게이트 트랜지스터의 구조를 비교했다.

그림 1. 트랜지스터 구조 비교

초소형 전자소자 패키징 기술

1. Single Chip Package on Substrate

이 기술은 각각의 전자회로 칩을 초소형 전자소자에 내장해 이를 기판에 접속하는 방법이다.

반도체 칩을 패키징하는 방법은 초소형 전자소자 재료에 따라 3가지로 구분된다. 수지 몰드 처리된 초소형 전자소자, 세라믹계 재료에 의한 초소형 전자소자 및 금속계 재료에 의한 초소형 전자소자가 그것이다.

다이 본딩 공정은 우선 리드 프레임에 칩을 고정한다. 칩 고정에는 Pd, Ag, 글라스 등의 미소 입자를 에폭시 계열 수지와 바인더에 혼합한 접착제를 사용하는 방법과 리드 프레임에 코팅된 배선(Au) 막과 칩(Si)과의 Au/Si 공정반응을 이용해 고정시키는 방식이 있다.

이들 중 공정반응으로 고정하는 방법을 주로 사용한다. 리드 프레임의 리드부와 칩 전극을 연결하는 와이어 본딩 공정이다. 여기서는 통상 Au 와이어를 이용해 칩 전극인 Al 막과 리드의 Au 부분을 연결한다. 일반적으로 Al 막은 대기 중에서 산화되기 때문에 열, 압력 및 초음파를 가해 Ai-Au 반응의 고상 확산을 유도한다. 이 방법은 많은 접합 기술 중에서도 가장 오래된 기술이며 현재까지도 널리 사용되고 있다. 이 과정이 끝나면 칩, 와이어 및 접합부를 전기적 및 기계적으로 외부 환경으로부터 보호하고 사용자가 사용하기 쉽도록 수지로 봉지한다. 이후 기판과의 접속공정은 리드 스루(Lead Through) 패키징 타입과 표면 패키징(SMT, Surface Mount Technology) 타입으로 나뉜다. 리드 스루 패키징 타입은 삽입 기기에 따라 기판 배선 일부에 사전에 관통 홀(Through hole)을 내어 놓은 곳에 초소형 전자소자 리드 선을 삽입하고 리드가 돌출된 뒷면에서 공정 납땜기(solder)를 사용해 플로우 납땜기로 고정시킨다.

한편 표면 패키징 타입은 기파의 리드 접속 부위에 솔더 페이스트를 인쇄하고 초소형 전자 소자를 정밀하게 올려놓은 후 역류 로(reflow furnace)를 통과시키면 납땜 접속이 이루어진다.

현재는 표면 패키징(SMT) 타입이 주로 사용되며 휴대전화, 정보 단말기기 및 수요 창조형 상품에 이용된다.

1980년 리드 스루 패키징 방법에서 SMT 방법으로 바뀌면서 패키징 면적, 전기 특성, 설계 및 생산성 등 많은 분야에서 변화를 가져왔다. 예를 들어 1980년 전후 10년 동안 리드 간격은 1.0㎜에서 0.5㎜로 좁아졌으며, 칩의 부품 면적도 약 20% 정도 줄었다.

CSP(Chip Size Package) 패키징 기술은 1990년대 들어서 대형 컴퓨터 분야의 소형화, 수요 창조형 가전 상품의 필요성, 멀티미디어 구성 등의 시대적 배경과 함께 MCM(Multi Chip Package on Substrate Module)이 크게 화재가 되고 있다.

그러나 MCM의 개발 실용화 과정에서 인프라, 코스트 및 설비투자 등의 문제점이 제기되어 CSP가 개발되기에 이르렀다.

CSP는 기존 SMT 프로세스를 기초로 하면서 소형화가 가능하다는 점에서 쉽게 받아 들여졌다. 이 기술은 휴대전화의 슬림화 및 경량화에 기여하고 있다. CSP 기술을 이용함으로써, 기존의 QFP(Quad Flat Package)에 비해 면적이 40∼70% 정도 감소했고, 중량 면에서도 그 이상의 감량 효과를 나타냈다.

하지만 이 기술은 초소형 전자소자에서 LSI 비율이 증대될수록 기판과 초소형 저자소자의 열팽창률 차이가 현저히 난다는 단점이 있다. 따라서 신뢰성 향상을 위해 초소형 전자소자 전극 구조 및 재료, 기판 디자인·구조·재료와 패키징 프로세스 등에 대한 연구가 지속돼야 할 것으로 보인다.

2. Multi Chip Package on Substrate

이 기술은 몇 개의 반도체 칩을 고밀도로 1개의 기판에 올려놓고 각각을 서로 연결해 1개의 초소형 전자소자로 기판에 접속하는 방법이다.

단일 기판에 능동소자와 수동소자를 집적화시켜 본체 기판에 부착시키는 구조인 하이브리드 집적회로(IC)는 오래전부터 실행해 왔다. 대표적인 하이브리드 집적회로의 예는 세라믹 기판의 Ag/Pd나 Au 등의 후면 배선에 IC를 다이 본딩 및 와이어 본딩 처리하고, 더욱이 저항, 콘덴서도 후막과 칩 부품으로 내장한 것이다.

이러한 기술은 자동차나 오디오회로 등에서 사용된다. 이는 MCM의 일종이라 할 수 있다. MCM은 비용이 다소 비싸지만 대형 컴퓨터에서 반도체 소자의 고속 성능을 가장 효과적으로 발휘할 수 있기 때문에 발전되어 왔다. 최근에는 가전 및 정보기기로의 적용도 시도되고 있다.

전자기기의 디지털화로 인해 LSI 비율이 증가하고 회로 동작 속도의 향상도 요구되기 때문에 LSI 소자를 가능한 한 고밀도로 유지하면서 방열 효과를 높이고 고속 동작이 가능하도록 구성해야 한다. 이를 실현하기 위한 기술 중 하나가 바로 MCM이다.

MCM의 요소 기술은 LSI를 노출형 칩 상태로 제작하는 기술, 기판기술, 방열 기술 및 패키징 기술이다. 이들 기술은 가전용, 사무 자동화(OA)용, 대형 컴퓨터용 및 통신용 등 여러 가지로 분류된다.

노출형 칩 접속 기술은 와이어 본딩, 테이프 자동화 본딩(TAB, Tape Automated Bonding), 플립칩 본딩(FCB, Flip Chip Bonding)이 이용되고 있다.

또한 기판 제조기술은 실리콘, 금속, 세라믹 및 글라스 에폭시 등의 재료위에 다층화한 기판을 이용하는 경우가 많다. 이에 방열을 위해 AIN 재료나 금속판을 유효하게 구조화한 것이 검토되고 있다.

결국 이와 같은 기술 요소들을 목적에 맞게 어떻게 조합하는 지가 MCM의 최대 관건이라 할 수 있다.

3. Bare Chip on Substrate

이 기술은 직접 반도체를 기판에 접속하는 방법이며, 노출형 칩을 직접 기판에 탑재하는 기술로는 와이어 본딩 방식, TAB 방식 및 플립칩 본딩 방식이 있다.

와이어 본딩 방식은 LSI 소자의 Al 전극과 기본 배선 전극을 배선으로 연결하는 기술로서, 가장 오래된 기술이다. 재료로는 Au, Al을 주로 이용한다.

와이어 본딩 기술은 와이어에서 분리된 반도체칩을 전극 처리하지 않고 사용할 수 있으며 기술도 확립되어 있기 때문에 적용 용도가 넓다.

TAB 방식은 배선을 형성한 필름 케리어 테이프(Film Carrier Tape)에 반도체 칩을 부착(ILB, Inner Lead Bonding)하고 표면부를 간단히 수지 코팅한 후 이를 기판에 접속(OLB, Outer Lead Bonding)하는 방식이다.

ILB는 테이프의 디바이스 홀 부위에 금속 코팅된 Cu 리드선과 LSI 소자의 Al 전극 사이에 돌기물을 삽입해 접속한다. 돌기물은 범프(bump)라 하며, 칩 쪽에 구성하는 것이 일반적이다. OLB는 외측 리드(Outer Lead)를 일체화하는 포밍(Forming) 방식과 비일체화하는 포밍리스(Formingless) 방식이 있다. 포밍 방식은 응력을 완화시키는 구조로 되어 있으며 정밀도가 높은 리드를 이용해 피치가 작은 접속에 적합하지만, 포밍 시 금형이 필요하기 때문에 관리에 주의가 필요하다.

포밍리스 방식은 응력에 대해서는 상대적으로 약하지만 금형이 불필요해 생산하는 측면에서는 좋은 시스템이다. 이 방식은 QFP에 비해 패키징 면적이 1/4, 두께 1/10, 중량 1/70 정도밖에 되지 않는다.

플립칩 본딩 방식은 칩 전극에 돌기를 만들어 배선 기판 전극에 접합하는 기술이다. 이 기술은 1963년 IBM사 컴퓨터에 채용한 SLT(Solid Logic Technology)로 거슬러 올라간다. SLT는 Cu 볼을 칩쪽에 형성해 기판의 전극과 가열 용융 접합하는 기술이며, 이 기술이 후에 C4(Controlled Collapse Chip Connection)라는 형태로 발전했다.

솔더 범프 형성법은 금속재 마스크를 이용한 증착법, 포토 프로세스(Photo Process)를 이용한 코팅법, 솔더 와이어에 의한 볼 본딩(Ball Bonding)법 등이 있다.

지금은 포토 프로세스를 이용하는 코팅 법이 주류이며, 불활성 분위기 중에서 가열 용융시켜 솔더의 표면 장력으로 원형의 전극을 형성한다.

솔더 범프 구성은 칩의 Al 전극에 직접적으로 솔더를 형성하지 않고 밀착성, 상호 확산, 솔더 흡착 등을 고려한 중간 금속재 층을 삽입해 솔더를 형성하지만 중간 금속재의 구성은 Cr-Cu-Au, Al/Ni-Ni-Cu 등이 실용화되고 있다. 기판 재료로는 과거 세라믹이 일반적이었지만, 최근에는 수지계 회로기판에 관심이 집중되고 있다.

21세기 반도체 패키지 기술

1. 패키지 형태의 혁신…시스템화 모듈 기술

고밀도 시스템화를 목표로 한 것으로 3차원 적층 모듈이 주목받고 있다. 과거 동일 패키지(예, DIP, Dual Inline Package 및 TCP, Tape Carrier Package)를 3차원 적층한 구조는 메모리 대용량화를 위한 피키지 레벨 3차원 적층 모듈로서 개발됐지만, 최근에는 칩을 적층해 하나의 패키지에 올린 칩 레벨의 3차원 적층 모듈이 개발되어 휴대전화용을 중심으로 양산되고 있다.

특히 플래시 메모리와 SRAM을 적층한 Stacked CSP는 휴대 전화용의 주류가 되고 있다. 앞으로 더욱 고밀도화 및 고성능화를 현실화하기 위해 다수의 칩을 탑재해 보다 고도로 모듈화한 3차원 적층 복합 모듈이 실용화될 것으로 예측한다.

또한 Si 칩에 관통홀을 뚫어 쌓아 올리고 관통홀을 통해 칩 간 전기적으로 접속한 3차원 적층 타입, 혹은 Si wafer에 관통홀을 설계해 전기적 접속한 웨이퍼 레벨 3차원 적층 타입도 개발 중이다.

2. 프로세스 혁신

패키지의 저비용화를 목표로 하는 혁신적인 프로세스도 개발되고 있다. 이는 웨이퍼 레벨 패키지로서, 최근 소개되고 있다. 이 프로세스 기술에 의한 패키지 가격은 웨이퍼당 양품 수에 따라 좌우된다.

완성품은 웨이퍼 레벨 CSP라고 부르나 외형적으로는 FBGA(Fine-pitch BGA)이다. 즉 Real Chip Size가 되어 플립칩과의 경계를 허물 수 있는 영역이 된다. 반도체 패키지가 칩의 재배선 프로세스 영역까지 올라온 시초가 된다는 의미로 보면 획기적인 기술이라 할 수 있다.

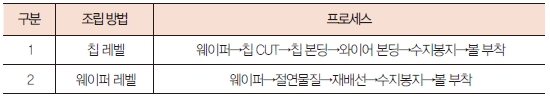

칩 레벨과 웨이퍼 레벨 패키지의 프로세스를 표 3에 비교했다.

표 3. 21세기 반도체 패키지 기술 프로세스 비교

3. 메모리용 패키지 구조

향후 DDR4는 그래픽 메모리나 통합 시스템 패키지에 사용되기 위해서는 1GHz 이상의 속도를 충족해야 한다. 지금은 BOC 구조를 개선해 사양을 맞출 수 있지만 앞으로 개발될 메모리의 패키지는 현재 Interconnection 방식인 와이어 본딩을 플립칩 범프로 바꾸거나 칩 위에 직접 배선을 형성하는 웨이퍼 레벨로 발전될 것으로 생각된다.

또한 메모리에 사용될 범프는 일반적인 솔더를 사용하는 C4 범프와 달리 금이나 구리 필러 또는 Stud 범프를 사용해 개발되는 것이 가격 경쟁력 면에서 바람직해 보인다. 이 경우 플립칩 본딩 방식이 달라져 기판의 표면 처리방식 또한 변화가 있을 것으로 예상된다.

더불어 기존의 와이어 본딩을 사용하는 CSP 기판의 Design Rule과 유사한 표준에 Soft-Gold 대신에 Lead-Free용 Sn을 전해 또는 무전해 표면처리 하는 방식이 등장할 것으로 보인다.

1GHz 이상의 고속 동작을 목적으로 하기 때문에 기판은 4-Layer 정도가 표준으로 사용되겠지만 전기적인 특성치를 맞추기 위해서는6-Layer 이상의 것도 사용될 것이다.

Layer간 구조나 비아의 크기는 Impedance Matching을 위해 스택 비아 형태의 Coreless 구조를 가지는 것이 필요해 보인다.

장동규 한국마이크로전자패키징연구조합