각종 Build-Up

공법과 용어설명

장동규 한국마이크로전자패키징연구조합

지난 호에는 공정별 작업 시 문제점 및 개선 사항과 B²iT, ALIVH 등 Build-Up 공법에 대해 알아봤다. 이번 호에서는 지난 호에 이어 NMBI, PVI, RCC, TCD 등 공법과 Conformal Mask, Direct Drilling 법에 대해 알아본다.

Build-Up 공법 : NMBI

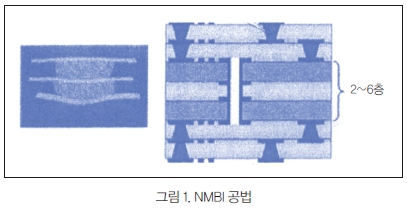

NMBI(Neo Manhattan Bump Inter Connection) 공법은 B²it 공법을 변형한 것이다.

NMBI 공법이 소개된 배경을 보면 전자제품의 경박단소화에 따른 Micro Via-Hole과 Fine Pattern 형성에 있어서 기술적·가격적인 측면에서 한계를 보임에 따라, 이를 극복하기 위해 Build-Up Process 중 혁신적인 기술개발과 이를 수용하기 위한 대규모 설비투자가 병행되어야 했다. 결국 이러한 과제를 해결하기 위해 Manhattan Bonding 공법을 채택한 NMBI 공법이 제안됐다.

이 공법은 동으로 Bump가 형성된 Copper Foil을 이용하며, 기존 공법인 Mechanical 또는 Laser Drill로 가공하고 도금해 층간 신호를 연결하던 부분을 Copper Bump로서 그 기능을 대체하는 Inter Connection 기술이다.

이 공법의 특징은 다음과 같다.

· 균일한 Bump의 높이 유지

· 극소경(40∼200㎛) Bump 제작

· 균일한 Cu Foil 두께 유지

· Bump와 Cu Foil과의 우수한 접착력

Bump가 Solid Metal로 구성되어 있기 때문에 기존의 전도성 Paste 또는 Cu Plating보다 우수한 열 전도성 및 저 저항치 실현

NMBI 공법에서 Bump는 다음과 같이 형성한다.

Cu-Ni-Cu층으로 이루어진 3층 재의 Foil에 Photo Resist Film을 이용해 Bump Pattern을 형성하고 Etching 액으로 부식시켜 Bump Foil을 제작한다.

이후 Bump의 형성 상태, 즉 Bump의 직경, 진원도 및 Bump의 손상 유무를 AOI 검사를 통해 확인하고 ‘B’ Stage 상태의 Prepreg를 이미 형성된 Bump Foil에 부착한 후 Prepreg 상층부로 돌출된 Bump를 제거한다.

그리고 별도의 Process로 이미 Pattern을 형성한 Core 층에 자동 Alignment 방식을 이용해 내층 Core와 Prepreg가 부착된 Bump Foil을 Lay up한 후 적층 Hot Press로 일치화시킨다.

이 같은 방식을 거쳐 다층의 Staggered Bump 접속 층을 제작할 수 있다. 이때 Bump Foil 층과 내층, 패턴 층을 수평적으로 작업할 수 있으므로 설비의 가동률을 극대화할 수 있으며, 제조 Lead Time 또한 단축할 수 있다(그림 1).

Build-Up 공법 : PVI

PVI(Photo Via) 공법은 미, 일 등 선진 PCB 업체를 중심으로 도입되고 있는 첨단 PCB 제조기술 중 하나로써 휴대폰 등 첨단 정보통신기기에 일부 적용되고 있는 Build-Up 기법의 아류 공법을 말한다.

이 공법은 일본 NEC가 ‘시바가이기사’의 잉크를 이용해 최초 개발했으며 RCC 기법보다 앞선 차세대 기술로 빌드업 기판 제작에 필수적인 레이저 드릴과 RCC 원판이 필요 없기 때문에 설비 투자비가 줄어들어 수율을 크게 향상시킬 수 있다. 또한 절연 수지가 가미된 특수 현상잉크를 절연층으로 사용·적층하는 기법으로 기술만 축적하면 신규 설비투자 없이 빌드업 기판을 제작할 수 있다.

하지만 열충격 및 내충격이 약하고 절연체의 층간 접속력과 설계 자유도 면에서 한계가 있다는 단점이 있다.

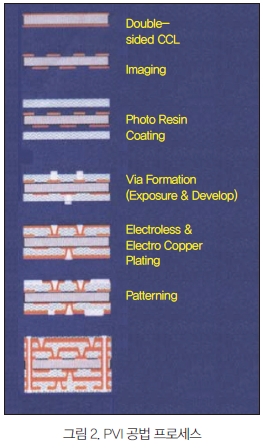

그림 2에 PVI 공법의 프로세스에 대해 나타냈다.

Build-Up 공법 : RCC

RCC(Resin Coated Copper) 공법은 Build-Up 층의 층간 절연층으로 Resin이 가미된 Copper Foil을 소재로 Laser 가공성이 우수하게 구성된 특수 재료를 사용해 층을 쌓아 올리는 기술로써 현재 대부분의 Build-Up 기술에 보급되고 있다.

이 공법은 양면 PCB 위에 RCC 원판을 압축·가열해 붙인 후 Via Hole이 뚫릴 부분을 에칭하고 Laser Drill로 관통해 Via Hole을 만든다. 이후 Via Hole에 동 도금하고 회로 형성을 위한 에칭까지 하면 1층이 완성된다.

이를 반복해서 적층하는 방법이며 반대쪽면도 같은 방법으로 적층한다.

이 방식의 특징으로는 제품의 취급성, 유변학적 특성, 레이저 홀 가공성 등이며 Laser Drill 가공성이 좋아 널리 사용되고 있지만, 원재료가 비싸다는 단점이 있다.

현재 Build-Up PCB의 핵심소재인 RCC는 모바일 기기의 소형화, 경량화, 고집적화, 다기능화 추세에 맞춰 향후 꾸준한 성장이 예상되지만 RCC가 불필요한 Build-Up 신규 공법들이 등장하고 있어 향방이 주목되고 있다.

이 공법을 사용함에 있어서 유의 사항은 다음과 같다.

· RCC 보관 : 보편적으로 Life Time은 20℃ 이하일 때 1개월, 5℃ 이하일 때 3개월이다.

· RCC 취급 시 : RCC는 Resin(B-Stage)과 Copper로만 구성되어 있기 때문에 취급 시 매우 조심스럽지 않으면 파손의 우려가 있다.

· RCC 적층 시 : 한 장씩 떼어내 전량 세정 후에 사용한다. 그 이유는 동박 면에 묻을 수 있는 Resin을 제거하기 위해서인데, 만약 세정을 하지 않고 작업한다면 Dent 불량을 유발할 수 있다.

· RCC가 PNL Size보다 클 경우 : PNL 가장자리(자삽바)의 동박 주름 불량이 발생할 수 있는데, 이럴 경우에는 조심스럽게 RCC를 잘라내어 사용해야 한다.

· RCC 공법은 Press 시 Resin Flow를 어떻게 제어하느냐에 따라 Resin Void와 같은 불량을 예방할 수 있다. 따라서 Press 후의 Resin 두께를 예상해 RCC의 규격을 결정해야 한다. 그렇지 않을 시 Short 불량을 유발할 수 있다.

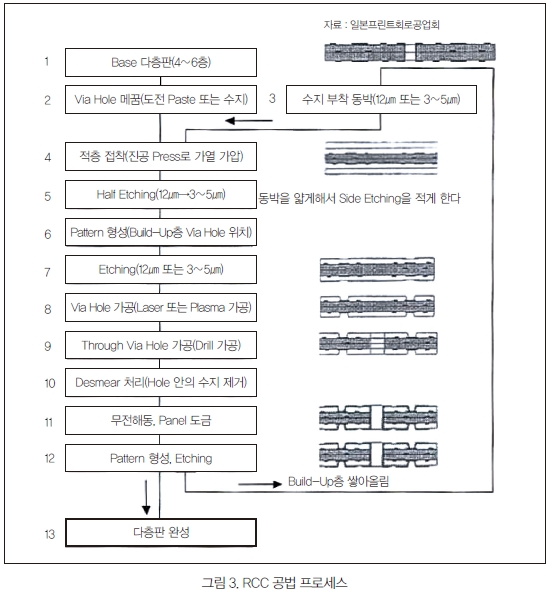

이와 관련해 RCC 공법의 Process를 그림 3에 나타냈다.

RCC는 수지부착 동박이라고도 하며, 이는 전해동박상에 절연성 수지를 코팅한 것이다. 이 수지는 Build-Up 층의 층간 절연재료가 되는 것으로 기존 Process에서 Prepreg에 해당한다. Prepreg와 다른 점은 이 수지층이 수지 단체에서 구성되고, Glass 섬유 등의 재료(보강재)가 들어가지 않는다는 것이다. Via Hole의 가공에는 Laser 가공, Plasma 가공이 이용된다.

RCC 공법에 대해 자세히 살펴보면 다음과 같다.

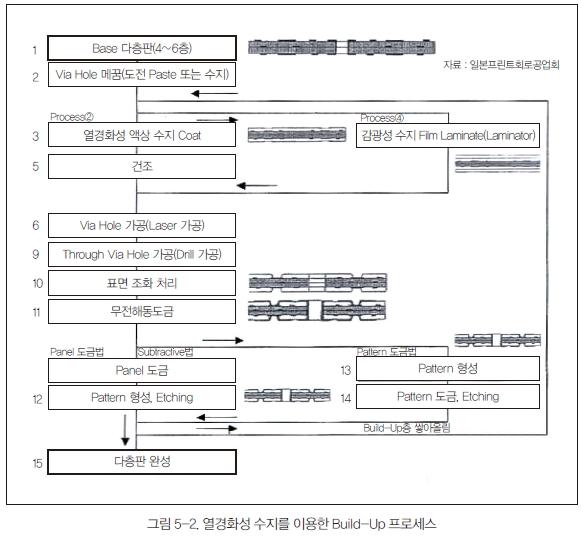

Base 다층판에는 종래법(표준 프로세스)으로 만들어진 통상 4∼6층 판이 사용되는데, Base 기판의 외층은 Build-Up 층의 1층이 된다. Base 기판에는 통상 도금 Through Hole의 Hole이 뚫려있으나, 이 위에 Build-Up 층을 형성할 수 없으므로 수지 또는 도전 Paste로 Hole을 충진하여 표면을 평활하게 한다(그림 3의 step 2).

수지부착 동박을 Base 다층판에 적층·접착해 Build-Up 층용 도체 층으로 한다(그림 3의 step 4). 적층에는 진공 Press를 사용한다.

이후 Build-Up 층용 Blind Via Hole과 Board 전체를 관통하는 Through Hole을 가공한다. Via Hole의 가공법에는 2종류가 있는데, 최근에는 대부분 Laser 가공을 주로 사용한다. Through Via(관통 Via)는 Drill 가공된다. Etching으로 Fine Pattern을 형성하는 경우에 동박 두께가 얇은 것이 유리하므로 Via Hole을 가공하기 전에 Half Etching 공정을 더할 수도 있다.·

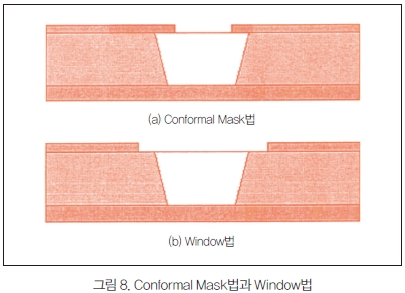

일반적으로 Via Hole을 Laser 가공할 때 소정의 위치에 소정 크기로 가공하기 위한 제어에는 Conformal Mask 법과 Direct Drilling 법이 있다.

Conformal Mask 법은 기판상의 동박에 희망하는 Via 경에 맞춘 경을 Etching하고 이를 창(mask)으로 해 Laser 가공하는 것이며, Direct Drilling 법에서는 동박 창을 사용하지 않고 Laser 위치 결정만으로 소정의 위치에 소정의 형상 Via를 가공한다.

RCC 공법에서 출발하는 Build-Up 공법에서는 Confor-mal Mask 법이 일반적이지만, Direct Laser Drilling 법도 가끔 사용된다.

수지 부착 동박을 적층한 Panel 상에 Via Hole 부를 남기고 전면을 Resist Pattern으로 덮어 Via Hole 부만 Etching Laser 가공의 Mask로 한다.

보통 Laser 가공한 Via의 Hole 안쪽은 용융한 수지(수지 smear)가 남아 있는데, 이를 제거하지 않으면 Via Hole의 무전해동, 전해동도금에 의한 층간 접속 신뢰성이 저하된다.

Via hole 가공법 중 Plasma 가공에 대해 간단히 설명하려 한다.

Plasma 가공에서는 기체 분자를 전이, 활성이 강한 이온을 이용해 노출한 절연물을 분해·제거한 후 Hole을 만든다. Plasma 가공 시 Panel을 진공 중에 두고 하며, Conformal Mask 법과 마찬가지로 Panel의 동박을 부분적으로 Etching해 가공 Mask로 사용한다. Hole 수에 관계없이 Plasma 가스로 가공할 수 있으므로 Hole 수가 많을 때 유리하다.

Desmear 처리 후 무전해동도금, 전해동도금, Pattern 형성, Etching을 해 Build-Up 1층분의 제조 Step이 완성된다. 통상 Panel의 양면에 Build-Up 층을 형성하므로 위 아래 합쳐 2개의 Build-Up 층이 형성된다. 만약 층을 더 쌓으려면 또 한 장의 수지 부착 동박을 Panel 상에 적층해 4∼12의 제조 step을 반복하면 된다.

마지막으로 요약하자면 수지부착 동박(RCC) 공정의 장점은 절연층이 이미 균일한 두께로 형성되어 있으므로 Build-Up 층의 층간 두께를 Control하기 쉽고 신뢰성 확보 및 특성 Impe-dance 제어가 용이한 점을 들 수 있다.

또한 Laser 가공기 외에는 기존의 다층판 설비를 이용해 비교적 간편히 Build-Up 기판을 제조할 수 있다는 점도 큰 장점이다.

반면 단점도 존재하는데, 동박과 Panel 도금을 Etching하는 Subtractive 법에 의해 도체 Pattern을 형성하므로 Fine Pattern의 형성에 한계가 있다는 점이다. 또한 Conformal Mask 법에서는 도체 Pattern의 Etching과는 별도로 Mask 용 동박 Etching이 필요하다는 점도 단점으로 꼽힌다.

이러한 단점을 극복하려면 Fine Pattern 형성에 관해서는 극박동박(약 3㎛)을 사용하고, Via Hole 가공에 관해서는 UV Laser 등에 의한 Direct Drilling 법 채용, 그리고 수지부착 Process에서도 Line/Space 50㎛ 이하를 권장한다.

Build-Up 공법 : TCD

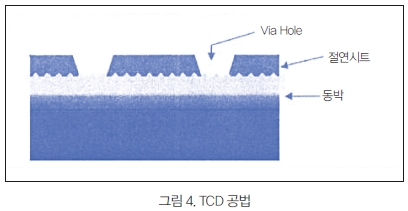

열경화성 수지공법인 TCD(Thermal Curable Dielectric) 공법은 코어 원판에 액상의 에폭시 수지를 도포한 후 경화시켜, 그 위에 무전해 동도금 방식으로 동박 회로를 형성하는 기법이다. 이 공법은 값비싼 RCC가 필요 없고 Press 등의 장비도 사용되지 않아 초기 설비 투자가 적게 들며, 초박 MLB를 제작할 수 있다는 이점이 있다(그림 4).

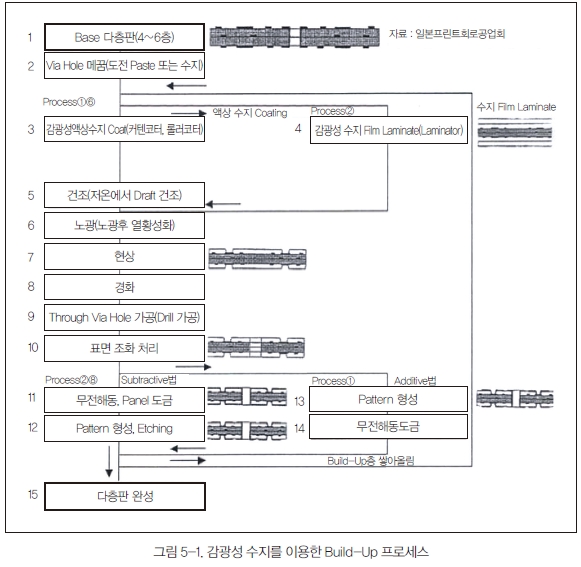

아래 열경화성 수지를 사용한 것과 감광성 수지를 사용한 Build-Up Process에 대해 그림으로 나타냈다(그림 5-1, 5-2).

Build-Up 공법 : CVF

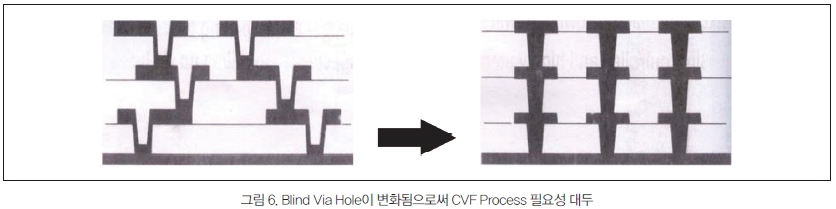

CVF(Copper Via Fill) 공법은 Blind Via Hole의 적용으로 인해 PCB가 더욱 작아지고 밀집도가 높아짐에 따라 Stacked Via Process를 적용함으로써 밀집도를 더욱 높일 수 있게 되면서 CVF Process에 대한 필요성이 대두됐다(그림 6).

이 공법은 Throwing Power가 우수하고 Packaging이 자유로우며 Wafer 개발이 용이하다.

제작 시 쉽게 제어될 수 있어야 하며 안정성을 갖추는 것이 포인트이다.

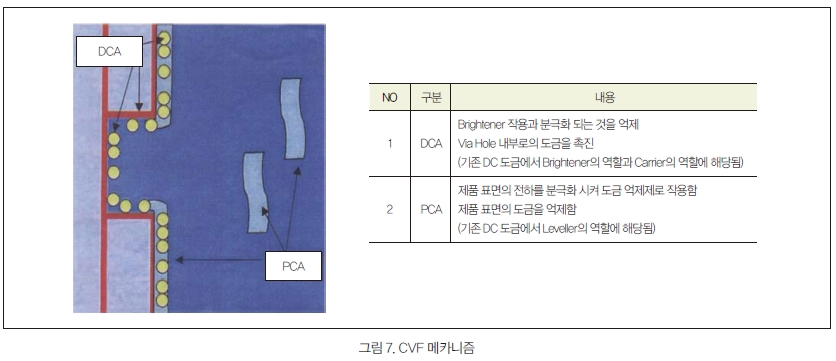

CVF의 메커니즘을 DCA와 PCA로 나누어 설명하려 한다 (그림 7).

그림 7에서 PCA는 표면 도금이 되는 것을 억제하며, DCA는 홀 속 도금을 촉진해 Via Filling이 된다. 여기서 Bath는 패턴 도금과 판넬 도금 등 두 가지로 나누어 볼 수 있다.

패턴 도금은 Low Metal/High Acid, 판넬 도금은 High Metal/Low Acid의 특성을 갖는다.

CVF의 프로세스는 다음과 같다.

· DI Water Rinse → Soak Clean → DI Water Rinse → Activate with 10% Sulfuric Acid → DI Water Rinse → Soft Etching → DI Water Rinse → Predip DCA → Galvanomeister CVF

Conformal Mask

Conformal의 Conform은 ‘맞추다, ‘투영하다’라는 의미이다. 기관 상의 동박에 희망하는 Via 경으로 맞춘 크기를 Etching하고, 그것을 창(Mask)으로 하여 Laser 가공한다. Mask 경보다 큰 범위의 Laser 빔으로 조사하지만 최종 크기는 Mask경으로 결정된다.

Conformal Mask 법의 변형이라고 할 수 있는 것 중 Mask경보다 작은 Via를 가공하는 방법인 Window 법이 있다. Window 법에서 Via를 가공하면 Hole의 가장자리에 동박 차양이 남게 되므로 Conformal Mask 법의 난점 중 하나인 미세 Via 도금을 쉽게 할 수 있다는 장점이 있다(그림 8).

1. Conformal 작업 조건

· Conformal 작업 조건은 다음과 같다.

· N/C Drill 후 도금 공정의 유입을 방지해야 함(1.0ø Hole 기준, 3쌍으로 구성)

· Conformal 작업 시 우선 Master Film의 막면/비막면을 확인한 후 이상이 있다면 바로 재출력한다.

· Laminate 시 PNL 전체에 Dry Film을 입힌다. 이때에는 아직 도금 전이기 때문에 PNL보다 작게 Laminate 될 경우 2차 Trimming이 불가피하다.

· 노광 작업은 Hole Size에 영향을 적게 받도록 평행광 노광기에서 작업한다. 이때 Guide Pin은 사용을 자제하며, 광량 체크는 필수적이다.

· 초도품 노광 후 반드시 현상 테스트를 거쳐 진공 불량에 의한 Hole 미형성, Hole 상태 불량 등을 방지한다.

· 부식은 반드시 가장 빠른 속도(6.1m/min) 내지는 부식 Chamber 4개만으로 작업한 후 반드시 Hole 경을 체크한다.

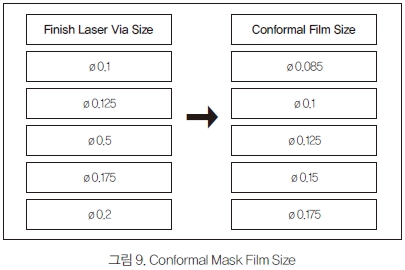

2. Conformal Mask Film Size

일반적인 Laser Drill Hole Size Tolerence는 ±0.1이다. Conformal 노광, Etching 과정에서 대개 Hole이 가장 빠른 Etching Speed에서도 25㎛ 정도 크게 나오기 때문에 Finish Hole Size에 맞추기 위해 Film Size를 작게 맞춰 공정에 제공하고 있다. 이는 Final Hole Size에 가깝게 함과 동시에 외층에서 LVH 터짐 등의 불량을 방지하기 위한 에뉼러링을 확보하기 위함이다(그림 9).

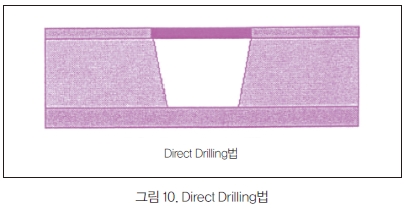

Direct Drilling

Direct Drilling 법은 동박 Mask를 사용하지 않고, Laser의 위치 결정만으로 소정의 위치에 소정의 형상 Via Hole을 가공하는 방법이다. 동박이 없는 절연재료에서 출발하는 Build-Up에서는 CO₂Laser로 Via를 가공할 수 있지만, 수지부착 동박에서 출발하는 경우에는 표면의 동박에 우선 Hole을 가공할 필요가 있으므로 UV Laser를 이용해 동박을 가능한 한 얇게 한 후 조화하고 CO₂Laser 가공하면 된다.

Hole 위치 정도는 Laser 위치 결정 정도에 따라 달라진다(그림 10).

각종 용어 설명

1. Aramid 섬유강화 CCL

아라미드 섬유는 아라미드 수지(방향족 폴리이미드 수지)로 만들어진 합성 섬유이며, 고내열성으로 합성 섬유 중에서는 상당히 고강도이기 때문에 방탄조끼나 소방복 등에 사용된다. 프린트 기판에 가장 널리 사용되는 동박적층판은 Glass 섬유 강화 Epoxy 수지 적층판인데, 그 Glass 섬유를 아라미드 섬유로 대체한 적층판이 아라미드 섬유 강화 동박적층판이다.

아라미드 섬유는 열팽창율이 마이너스(온도가 상승하면 수축함)라는 특이한 성질 때문에 Epoxy 적층판의 기재에 사용하면 기판의 열팽창률을 억제할 수 있다. 또한 섬유가 강하기 때문에 적층판의 Drill 가공이나 Router 가공은 일반적으로 Glass 섬유 강화 적층판보다 어렵다.

2. Bump

반도체 Chip의 랜드 위 혹은 테이프 캐리어(TAB)의 테이프 상에 올라온 금속 돌기부로 Inner Lead Bonding을 용이하게 한다. Inner Lead Bonding이란 기판이나 Bonding Tape 상의 도체와 Via Chip 상의 단자와의 사이를 접속하는 것이다. 결국 Bump란 혹이나 융기라는 뜻이다.

3. Inter Poser

LSI Chip과 프린트 기판과의 사이에 두어 LSI에서 나오는 배선을 재배치하고, 접속 단자의 배치를 변경하기 위한 기판 CSP는 Chip과 거의 같은 사이트이지만, Chip과 CSP에서는 단자의 배치가 항상 같지 않다. 그 이유는 프린트 기판의 설계에 사용되는 디자인 룰이 Chip에 비해 훨씬 크므로 Chip의 단자 배치 그대로 프린트 기판에 배선을 배치할 수 없기 때문이다. Interposer는 Chip에서 나오는 배선의 Fan Out을 담당한다.

4. 전사법

스테인레스판 위에 Pattern 형성, 전해동도금을 해 도체 Pattern을 만들고 이를 절연 기판상에 전사 접착함으로써 프린트기판의 도체 Pattern을 형성하는 방법이다. 더불어 Carrier Film 상의 동박을 Etching 해 도체 Pattern을 만들고 이를 수지 기판 상에 전사 접착하는 Process 또한 Build-Up 법으로 사용된다.

스테인레스판 위에 도체 Pattern을 만드는 방법은 Pat-tern 도금만으로 도체가 형성될 수 있으며, Etching이 불필요하므로 Fine Pattern 형성에 유리하다.

이 중 어떤 방법을 사용하든지 간에 도체 표면을 조화한 위에 전사하면 수지 기판과의 밀착성을 향상시킬 수 있다는 이점이 있다.

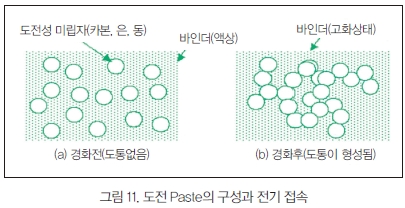

5. 도전 Paste

도전 Paste는 Carbon, 은, 동 등의 도전성 미립자를 점성이 있는 바인더에 고농도로 분산시킨 Paste를 말한다. 바인더에는 Epoxy 수지 등 열경화성 수지를 이용한다.

Paste 상태에서 도전성 미립자는 액상 바인더 안에 뿔뿔이 흩어져 다니며, 가열 경화할 때 수지가 수축하므로 도전성 미립자가 서로 기계적으로 접촉해 전기적인 도통이 발생한다(그림 11).

Prepreg는 경화 시 수축하지만 동시에 도전 Paste도 압착되어 접속의 신뢰성 향상에 도움이 된다.

도전 Paste로 형성된 도체의 저항은 일반적으로 금속 도체보다 100배 이상 높다. 따라서 Fine Pattern이 긴 표면 도체에는 쓰이지 않는 편이다. 그러나 주로 짧은 거리의 Jumper 선으로 혹은 Via의 Hole 충진 도통용으로 Through Hole 도금 대신 사용된다.

세라믹 다층판의 경우에는 텅스텐, 몰리브덴 등의 내열 금속 미립자의 Paste를 사용해 900℃ 정도의 고온에서 소성한다. 이때 유기 바인더는 날아가 버리고 금속 동사가 결합해 신뢰성 높은 전기 접속이 얻어진다.

유기 재료의 기판에서 Paste의 경화는 150℃ 전후에서 이루어지므로 결합 후에도 바인더가 남아있다. 또한 결합 후 미립자의 접촉면에 수지가 남아있으면 도통이 얻어지지 않고, 미립자 동사의 접촉이 불안정한 경우는 경시적으로 접속의 신뢰성이 저하되므로 확실한 접촉이 얻어지도록 Paste 조성, 사용 형태에 대한 연구가 필요하다.

6. 일괄 적층법에 의한 전층 Build-Up

· Bump 부착의 단면 또는 양면 Sheet를 접착제층을 넣어서 일괄 적층하는 방법이다. 동장 Glass Epoxy Sheet에 Laser Via를 가공해 동도금으로 주상 Via를 형성하는데, 그 위에 저 융점 금속(solder 등)의 Bump 도금을 입힌다. · 이후 제작한 Sheet의 전면에 Epoxy 접착제를 도포하여 복수 매의 Sheet를 일괄 적층하면 저 융점 금속 Bump는 용융된 Epoxy 접착층을 밀어내고 Land에 접속된다.

· 도전 Paste로 Via를 채운 Prepreg 위에 미리 도체 Pattern을 형성한 Film을 겹쳐 압착한 후 Film을 벗겨낸다. 이런 식으로 형성된 Sheet를 복수 매 일괄 적층한다.

· 동박 상의 Polyimide 와니스층에 Photo Via를 형성해 Bump 도금(동+금)을 형성한 Sheet를 복수 매, 접착층을 넣어서 접착하는 방법이다. Bump와 Land의 접합에는 초음파를 사용한다.

· 도전 Paste로 Via를 채운 Polyimide Film(접착제 부착) 위에 미리 도체 Pattern을 형성한 Carrier Film을 겹쳐 적층한다. 적층 후에는 Carrier Film을 벗겨낸다. 이를 반복해서 층 수를 늘려갈 수 있다.

· 접착제를 부착한 동장 Polyimide Film을 Etching해 도체 Pattern을 형성한다. 이후 표면에 Laser Via를 가공해 도전 Paste를 충진한다. 이러한 Sheet를 복수 매 겹쳐서 열 압착한다. 접착제, 도전 Pasted 모두 열가소성 Polyi-mide를 사용하므로 열압착시에 일체화되고 전기적으로 접속된다.

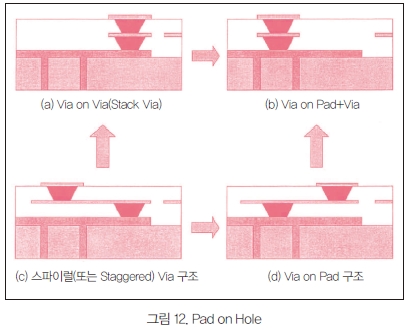

7. Pad on Hole

기존 다층판의 단점 중 하나는 관통 Via로 인해 배선이 필요 이상으로 자리를 차지하고 있다는 점이었다. 하지만 Build-Up 배선판에서는 접속을 필요로 하는 층과 층간만으로 Blind/Buried Via를 둘 수 있어 배선 밀도를 크게 높일 수 있다.

예외로 Build-Up 법 중에는 Blind/Buried Via의 배치에 제약 때문에 그림 12의 (a), (b)를 만들 수 없는 프로세스도 있다.

Via가 수지(혹은 도금)로 메워지지 않아 충진 수지가 연약하고 표면의 도체도 얇아 Via의 바로 위에 겹쳐서 Via를 형성할 수 없다. 이를 Via on Via, 혹은 Stack Via라고도 한다.

Via on Via를 만들 수 없는 경우에는 두 번째 Via를 그림 12의 (c) 같이 아래 Via의 바로 위가 아닌 조금 비켜서 배치해야 한다. 이와 같은 Via를 Staggered Via 혹은 스파이럴 Via라고 한다. 이처럼 Via의 배치에 제약이 있으면 배선에 이용할 수 없는 Dead Space가 생기므로 Blind/Buried Via를 사용해도 배선 밀도가 생각 외로 높지 않아 배선 회전이 길어져서 전기적인 성능에 영향을 미칠 수도 있다.

만약 Via on Via나 Via on Pad(혹은 그림 12의 (b), (d))가 가능해지면 배선 밀도가 크게 높아지므로 어느 Build-Up 법에 대해서도 문제없다.

결국 Pad on Hole은 도금 Through Hole에 수지 또는 도전 Paste를 채우고 그 위에 형성한 Pad를 나타내며, 이 Pad 상에 Via를 형성한 것이 Via on Pad이다.

이 같은 배치의 Via나 Pad를 형성하는 데에는 고신뢰성의 충진(VIa Filling), 표면 평탄화 및 조화 기술이 중요해 보인다.