연산 증폭기의 DC 오차 특성과, 오차 요인이 고정밀 애플리케이션에 미치는 영향

연산 증폭기는 외부 입력 신호에 정밀 이득을 적용하여 ‘입력×폐쇄 루프 이득’으로 증폭된 출력을 제공하는 2포트 IC이다. 여기서는 연산 증폭기의 입력 바이어스 전류, 입력 오프셋 전압, CMRR, PSRR, 입력 임피던스 등의 DC 오차 요인과 이것이 미치는 영향에 대해 살펴본다. 이 글을 읽으면, 이와 같은 오차 요인들이 고정밀 애플리케이션의 정확도에 어떻게 영향을 미치는지 이해할 수 있을 것이다.

Srudeep Patil Maxim Integrated

정밀 연산 증폭기는 낮은 주파수∼중간 주파수 대역에서 중간 DC 이득 수준으로 작동할 경우 이상적인 것에 가깝게 동작한다. 그러나 이와 같은 조건이라고 해도 기타 요인들에 의해 연산 증폭기의 성능이 영향을 받음에 따라 정확도에 영향을 주며 성능이 제한될 수 있다.

이러한 요인들 중 가장 일반적인 것은, 높은 DC 이득을 이용하는 애플리케이션에서 두드러지는 입력 참조 오차(Input Referred Error)이다.

여기서는 입력 참조 오차가 연산 증폭기에 미치는 영향에 대해 설명한다. 이러한 오차 요인들로는 입력 바이어스 전류, 입력 오프셋 전류, 입력 오프셋 전압, CMRR, PSRR, 유한 입력 임피던스 등이 있다. 실제로는 이 모든 오차들이 동시에 발생한다.

또한 데이터 시트의 EC(Electrical Characteristics) 테이블에 있는 연산 증폭기 성능 사양의 경우, 특별한 표기가 없는 한 이 테이블 상단에서 지정하는 조건으로만 보장한다는 점에 대해 디자이너들이 유의해야 하는 이유에 대해서도 설명한다.

실제 전원 전압, 동상 전압(Common Mode Voltage) 범위, 기타 조건들이 변하는 데 따라 이들 DC 오차가 미치는 영향 또한 변동적이다.

입력 바이어스 전류와 입력 오프셋 전류에 의한 오차(1)

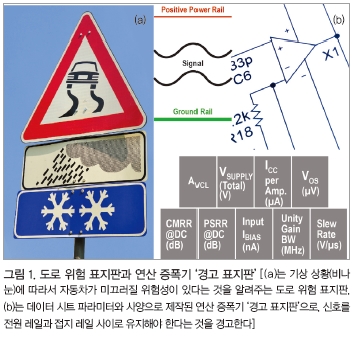

엔지니어들은 주변에 다양한 위험 가능성이 있다는 것을 잘 알고 있다. 그런데도 설계 시 피해야 하는 함정들이 있다는 점에 대해서는 간과하는 듯하다. 이 경우 연산 증폭기에 어떠한 영향을 미치는지 살펴보자[그림 1(a), 그림 1(b)].

그러면 2개의 기초적인 공식부터 시작해 보자.

IB=(IBP+IBN)/2 (1)

IOS=IBP-IBN (2)

IB는 입력 핀으로 흐르는 평균 입력 바이어스 전류, IBP는 양의 입력으로 흐르는 입력 바이어스 전류, IBN은 음의 입력으로 흐르는 입력 바이어스 전류, IOS는 입력 오프셋 전류이다.

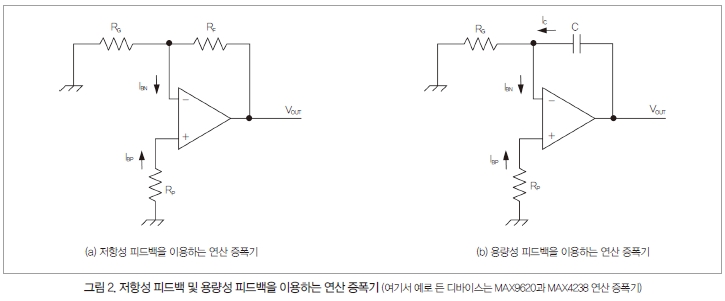

입력 바이어스 전류와 입력 오프셋 전류는 정밀 증폭기 애플리케이션에서 가장 중요한 두 가지 특성이다. 이들 전류는 저항성 피드백이나 용량성 피드백을 통해 출력에 영향을 미친다. 많은 반전, 비반전, 합계, 차동 증폭기는 동적 입력을 0으로 설정할 경우 그림 2(a)와 그림 2(b)로 나타낼 수 있다.

여기서는 설명의 편의를 위해서 모든 입력 신호를 0으로 설정하고 입력 전류가 출력 정확도에 미치는 영향에 대해 살펴본다. 또한 저항성 피드백[그림 2(a)]과 용량성 피드백[그림 2(b)] 회로에 대해서도 각각 살펴본다. 그림 2(a)에 중첩 원리(Superposition Theorem)를 적용하면 다음과 같이 된다.

VOUT=(1+RF/RG)×[(RF//RG)×IBN-RP×IBP] (3)

식 (3)에서 다음 내용을 추론할 수 있다.

입력 신호가 없으면 이 회로는 유한 출력 전압을 발생시킨다. 이 필요 없는 출력 오차를 출력 DC 잡음이라고도 한다.

출력 전압은 입력 오차 혹은 입력 DC 잡음을 (1+RF//RG)로 증폭함으로써 발생된다.

입력 DC 잡음은 두 가지 성분으로 이루어진다. IBP가 RP를 통과하여 흐를 때의 전압 강하와 IBN이 RF//RG 조합을 통과하여 흐를 때의 전압 강하이다.

애플리케이션에 필요한 정밀도 수준에 따라서 수동 소자 값과 연산 증폭기 둘 다 신중하게 선택해야 한다. 이것은 입력 바이어스 전류가 출력 정확도에 미치는 영향을 제거할 수 있는 가장 좋은 방법이다. 그러므로 RP=RF//RG가 되도록 선택하면 식 (4)를 도출할 수 있다.

VOUT=-(1+RF/RG)×(RF//RG)×IOS (4)

RP=RF//RG가 되도록 선택함으로써 출력 오차를 수십 분의 일로 줄일 수 있다. 하지만 센서 인터페이스가 높은 이득(100V/V 이상)으로 이루어진 고정밀 애플리케이션에서는 여전히 입력 오프셋 전류가 낮은 연산 증폭기를 선택하는 것이 바람직하다. 뿐만 아니라 RP를 추가하는 것이 현실적으로 항상 가능한 것은 아니다. 마지막으로, 입력 바이어스 전류와 저항 크기 둘 다 출력 오차에 있어서 매우 중요한 역할을 담당한다. 이 경우 디자이너는 입력 바이어스 전류와 입력 오프셋 전압이 낮고 속도 대 성능 비율이 낮으며 CMRR과 PSRR이 높은 연산 증폭기를 선택해야 한다.

더 낮은 RF와 RG를 선택하면 출력 오차를 더욱 더 낮출 수 있는데, 이 경우 회로의 전력 소모는 높아진다. 그러므로 저항의 크기를 선택할 때에는 출력 오차와 전력 소모를 신중하게 절충하고 적절한 균형점을 찾아야 한다.

그러면 이번에는 그림 2(b)로 돌아가서 살펴보자. 플러스 입력이나 마이너스 입력 모두 전압은 다음과 같다.

VIN+=VIN-=-RP×IBP (5)

여기서 VIN+는 비반전 입력의 전압이고, VIN-는 반전 입력의 전압이다. 반전 입력으로 키르히호프의 전류 법칙을 적용하면 다음과 같다.

VIN-/RG+IBN-IC=0 (6)

식 (5)를 대입하여 식 (6)에서 VIN-를 제거하면 입력 바이어스 전류와 피드백 커패시터를 통해 흐르는 전류에 대한 식인 식 (7)을 구할 수 있다.

IC=(RG×IBN-RP×IBP)/RG (7)

여기에 마이클 패러데이(Michael Faraday)의 정전용량 법칙을 적용하면 다음과 같이 된다.

VC=1/C∫IC dt (8)

여기서 VC는 커패시터상의 전압이고 이것이 바로 VOUT이다. 식 (8)에 식 (7)을 대입하면 식 (9)를 도출할 수 있다.

VOUT=1/(RG×C)×Integral(RG×IBN-RP×IBP)dt (9)

식 (9)는 그림 2(b)의 출력 전압 오차를 제공한다. 이 오차를 최소화하려면 RP=RG로 선택한다. 그러면 식 (9)를 식 (10)과 같이 간략화할 수 있다.

VOUT=-1/(C)×Integral(IOS) dt (10)

C와 IOS는 비교적 일정하므로 식 (10)을 시간에 걸쳐 적분하면 식 (11)을 얻을 수 있다.

VOUT=-IOS×t/C (11)

식 (11)에서는 전압이 상승하여 연산 증폭기를 포화 상태로 구동한다는 것을 알 수 있다.

VOS와 TCVOS로 인한 오차

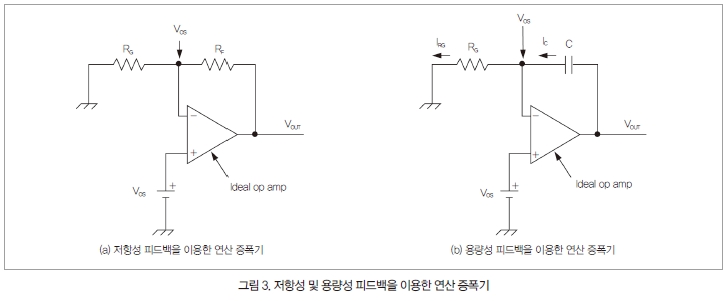

그러면 이번에는 연산 증폭기 회로에서 입력 오프셋 전압이 저항성 및 용량성 피드백에 미치는 영향에 대해 살펴보자. 그림 3(a)에서 출력 전압 오차는 다음과 같다.

VOUT=(1+RF/RG)×VOS (12)

여기서 (1+RF/RG)는 DC 잡음 이득이다. 저항이 클수록 이 오차가 커진다. 그림 3(b)에서 입력 바이어스 전류가 무시할 만큼 미미한 연산 증폭기라면 IC=IRG이다. 그러면 VIN-=VOS인 경우 IC=IRG=VOS/RG이다. 패러데이의 정전용량 법칙을 적용하면 식 (13)을 도출할 수 있다.

VOUT=Integral(VOS)dt/(RG×C) (13)

여기서도 식 (13)을 시간에 걸쳐 적분하면 연산 증폭기 출력이 VOS의 극성에 따라 어느 한쪽 레일로 포화된다.

식 (12)와 식 (13)에서 매우 중요한 한 가지 결론을 알 수 있다. 특정한 수동 저항 및 커패시턴스 값일 때 오프셋 전압이 누적 출력 전압 오차에 가장 큰 비중을 차지하는 요소라는 것이다.

그러면 예를 들어 살펴보자. 온도 변동이 일반적인 정밀 애플리케이션에서는, 오프셋 전압의 열 드리프트(TCVOS)와 입력 오프셋 전압이 매우 중요한 역할을 담당한다. 정밀 애플리케이션에서 연산 증폭기의 TCVOS의 중요성을 살펴보기 위해 보통의 연산 증폭기(최대 TCVOS=5㎶/℃, 최대 VOS=50㎶)와 MAX9620(최대 TCVOS=0.12㎶/℃, 최대 VOS=10㎶)을 비교해 보자. 이 때는 식 (14)와 같이 된다.

Maximum VOS(T)=max VOS(+25℃)

+maximum TCVOS×(T-25℃) (14)

그러면 MAX9620 연산 증폭기를 예로 들어 보자. 특정한 애플리케이션에서 온도가 실온(+25℃)에서 +125℃로 변화했다고 하면 열 드리프트(Thermal Drift)로 인한 최대 VOS는 식 (15)와 같다.

Maximum VOS(T)=10㎶+0.12㎶/℃×(100℃)=22㎶ (15)

이와 비교해서 50㎶ 최대 오프셋 및 5㎶/℃ 최대 TCVOS인 연산 증폭기는 식 (16)과 같다.

Maximum VOS(T)=50㎶+5㎶/℃×(100℃)=550㎶ (16)

이 결과를 보면 애플리케이션으로 높은 정확도가 요구될 때 입력 오프셋 전압의 열 드리프트가 중요한 요소라는 것을 알 수 있다(MAX44250과 MAX4238 증폭기 제품군 역시 각각 6㎶ 및 2㎶ 대의 최대 입력 오프셋 전압을 제공한다. 이것은 디지털 저울이나 기타 센서 프론트엔드 애플리케이션 등의 고정밀 mV 신호 레벨 증폭에서 요구되는 수준이다).

CMRR과 PSRR 한계로 인한 오차

통상적인 연산 증폭기에서 유한 CMRR(Common Mode Rejection Ratio)은 입력 오프셋 전압을 유발함으로써 정밀도를 떨어트린다. 증폭기의 CMRR이 높을수록 증폭기가 정격 입력 동상 전압에 걸쳐서 입력 오프셋 전압 변동에 대해 덜 민감하게 된다. 입력 신호가 수mV 대로 매우 낮은 애플리케이션에서는 높은 CMRR이 절대적으로 요구된다.

증폭기의 CMRR은 차동 이득(ADIFF) 대 동상 이득(ACM)의 비이다. CMRR은 또한 입력 동상 전압(VCM)이 1V 변화하는 것에 대해 입력 오프셋 전압의 변동으로서도 표현할 수 있다. 그러므로 식 (17)과 같다.

VOUT=ADIFF×[(VIN+-VIN-)+ACM×VCM/ADIFF] (17)

식 (17)을 다음과 같이 나타낼 수도 있다.

VOUT=ADIFF×(VIN+-VIN-)+ACM×VCM (18)

또한 다음과 같이 나타낼 수도 있다.

CMRR=ADIFF/ACM=delta(VCM)/delta(VOS) (19)

유한 PSRR(Power Supply Rejection Ratio) 역시 전원 전압 변동과 관련하여 추가적인 입력 오프셋 전압을 유발한다는 점에서 중요한 요소이다. 전원 전압(VCC)의 변동은 내부 트랜지스터의 작동 지점을 변화시키고 이것은 다시 입력 오프셋 전압에 영향을 미친다. PSRR이 높을수록 증폭기는 전원 전압이 변화하는 것에 따라 입력 오프셋 전압 변동에 대해 덜 민감해진다.

PSRR=delta(VCC)/delta(VOS) (20)

증폭기 데이터 시트의 EC(Electrical Characteristics) 표에서 제공하는 CMRR과 PSRR 사양은 특별한 표기가 있지 않은 한 각각 특정한 입력 동상 전압 및 전원 전압 범위일 때의 사양을 표기하고 있다. 그런데 데이터 시트에 표기된 CMRR 사양은 전체 전원 전압 범위에 걸쳐 동일한 것이 아니며, PSRR 사양은 전체적인 입력 동상 전압 범위에 걸쳐 동일한 것이 아니라는 점에 유의해야 한다(MAX44246, MAX44250, MAX9620 증폭기 제품군의 CMRR은 각각 158dB, 140dB, 135dB이고 PSRR은 각각 166dB, 145dB, 135dB이다. 고정밀 DC 성능이 필요한 애플리케이션에서는 반드시 매우 높은 CMRR과 PSRR이 요구된다).

입력 임피던스 한계로 인한 오차

연산 증폭기의 유한 입력 임피던스(RIN)는 증폭기를 구동하고 이득 오차를 유발하는 소스 임피던스(RS)와 전압 분할기를 형성한다. 그러므로 무시할 만한 미미한 오차를 달성하기 위해서는 수십 기가옴 대에 이르는 매우 높은 입력 임피던스가 요구된다.

VIN=VSOURCE×[RIN/(RIN+RS)] (21)

식 (18)에서 RIN>>> RS인 경우 VIN=VS이다.

결론적으로 입력 오프셋 전압, 입력 바이어스 전류, 유한 입력 임피던스 등의 DC 오차를 적절히 다루지 않으면 연산 증폭기 측정 정확도를 달성하지 못한다. 이것은 정확도가 무엇보다도 중요하게 요구되는 고정밀 애플리케이션에서는 결코 허용될 수 없는 것이다. 또 한 가지 중요한 점으로, 디자이너는 데이터 시트의 EC 테이블에 표기되어 있는 연산 증폭기 성능 사양의 중요성과 한계에 대해 충분히 이해해야 한다.

여기서 설명한 가이드라인들을 참조함으로써 디자이너는 자신의 애플리케이션으로 적절한 연산 증폭기와 적절한 구성의 수동 소자들을 선택할 수 있을 것이다. 또한 자신의 디자인에 적합한 연산 증폭기를 선택하면 연산 증폭기 오차를 없애고 최대의 정확도를 달성할 수 있을 것이다.