[헬로티]

후공정인 패키징 원가 낮추고, 반도체 고성능화에 따른 기술 변화 이끌어

현재 패키징 산업은 궁극적으로는 SIP와 원칩 모듈로 가는 과정에 있다. 현재는 시스템이 잘못되면 검증하고 PCB를 만드는 개발 과정을 다시 거쳐야 하는데, SIP나 원칩 모듈 수준까지 시장이 발전하면 제품 개발 리드타임을 크게 줄여 원가를 낮추게 됨은 물론, 두께와 부피도 대폭 줄일 수 있게 된다. 그리고 이러한 큰 흐름 속에서 FOWLP가 기존 패키지 시장을 대체할 게임 체인저로 부각되고 있다.

그 동안의 반도체 패키징은 에폭시 몰딩 컴파운딩형 패키징, PCB기반의 패키징이 일반적 형태였다. 국내 대기업의 모바일 반도체 패키징 역시 PCB기반 패키징으로, PCB 기반 AP (Application Process)를 북미 모바일 업체에 공급해온 바 있다.

그러나 점점 반도체가 다기능화 되면서 요구되는 핀(pin) 수가 많아지고 이에 따라 패키징 사이즈가 커지게 되었는데, 이에 따라 모바일, 웨어러블 디바이스 등의 제품이 추구하는 ‘경박단소’ 트렌드에 부합하는 패키징 니즈가 발생하게 됐다. 이러한 수요를 충족시키기 위해 개발된 기술이 Wafer Level Packaging(WLP)이다.

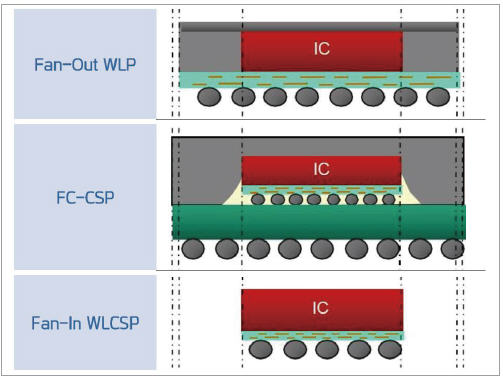

WLP는 웨이퍼에 직접 칩을 실장하는 기술이다. 이를 통해 반도체 두께 및 부피를 줄이는 혁신이 가능해졌다. 그리고 여기서 한 단계 더 발전한 기술이 Fan-Out Wafer Level Packaging (FOWLP)으로, 기존 Fan-In Wafer Level Packaging 보다 더 작고 성능이 고도화된 패키징 기술이다. 특히, 최근 북미 모바일 업체가 FOWLP 기반의 AP를 신규 모델에 적용하기로 결정하면서 FOWLP에 대한 관심이 빠르게 고조되고 있다.

반도체 패키지 패러다임 변화

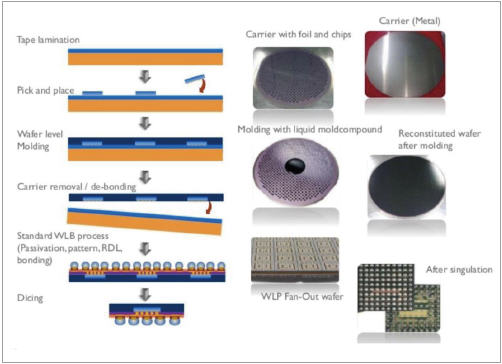

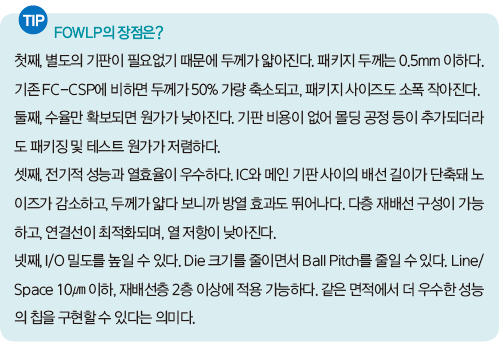

FOWLP이 주목받는 것은 반도체 패키지 패러다임 변화에서 이유를 찾을 수 있다. 패키지 시장에 대한 새로운 접근이 필요한데, 첫 번째 동향은 반도체 총원가가 상승하고 있고, 전공정(Front End)의 원가를 낮추는 데는 한계에 도달했기 때문에 후공정(Back End)인 패키징 원가를 낮춰야 하는 필요성이 커지고 있다.

반도체 생산이 미세 공정화되는 추세에 있어 28nm 이후로는 고가 설비 등으로 인해 제조 원가가 상승하고 있다. 시장조사기관 IBS에 따르면, 공정별 게이트 1억 개당 원가는 28nm가 1.4달러인데 비해, 20nm와 14/ 16nm FinFET 공정은 각각 1.42달러, 1.62달러로서 28nm 대비 1.4~15.7% 높은 것으로 분석됐다.

20nm 공정부터는 물리적으로 회로 선폭을 줄이는 데 상당한 어려움이 따르는데다 설계, 공정, 장비, 재료 비용도 큰 폭으로 늘어나기 때문에 28nm 공정보다 칩 면적이 축소돼도 원가는 오히려 상승하고 있다. 향후 극자외선(EUV) 노광 장비가 본격적으로 도입되고, 10nm 이하 반도체가 양산된다고 하더라도 원가를 낮출 수 있는 새로운 패키징 기술이 필수적이다.

두 번째 추세는 반도체의 고성능화로 인해 입출력(I/O) 단자 수가 증가하는 추세에 있다.

예컨대 갤럭시 S7에 탑재된 AP (Application Processor)의 I/O 단자 수는 갤럭시 S6 때보다 44% 증가한 것으로 파악된다. 제조업체들은 다이(Die) 사이즈가 작아지는데 반해 I/O Pin 수를 늘려야 하는 딜레마에 있어서 다이(Die) 표면의 더 많은 접속부를 위해 볼 패치(Ball Pitch)를 줄이거나 좀 더 쉬운 재배선을 위해 팬-아웃(Fan-Out)으로 진화해 가는 2가지 방안 중 선택해야 한다.

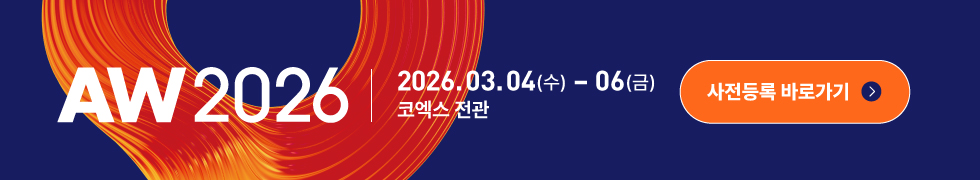

▲ 그림 1. FOWLP 개요

FOWLP, 반도체 패키지 소형화로 주목

기존 FC-CSP나 WB/FC-BGA는 I/O 밀도에 대응하다 보니 원가가 상승하고 있다.

업계에 따르면, 유사한 패키지 사이즈(13X13mm)를 기준으로 할 때 전형적인 I/O Pin 수는 리드 프레임(Lead Frame)과 Wire Bond BGA가 150~200개, FC-CSP가 900~1,000개 수준인데 비해 FOWLP는 1,400개 수준으로 늘어난다.

Wafer Level Package처럼 기판을 사용하지 않는 차세대 패키지 기술이 보급되기 시작하면서 기판 업체들은 수요 감소에 따른 생존 위기에 내몰릴 수 있고, 대안 기술 마련이 시급한 상태다. 파운드리 업체가 패키지까지 담당하기 때문에 반도체 전공정과 후공정의 경계가 모호해지고, 파운드리, OSAT(Outsourced Semi-conductor Assembly and Test), 기판의 영역이 통합되고 있다.

반도체 패키지는 칩 영역에 대한 패키지 입출력 단자의 위치에 따라 팬 인(Fan-In) 방식과 팬 아웃(Fan-Out) 방식으로 나뉜다. 대다수 패키지는 입출력 단자 사이의 간격에 큰 제한이 없는 팬 아웃 방식으로 설계된다. 팬 인 방식은 칩 사이즈가 비교적 커서 칩에 형성된 전극이 마더 보드에 형성된 전극과 동일한 간격으로 대응되는 경우에 적용되는 구조다.

반면, 팬 아웃 방식은 칩 사이즈가 작아서 칩에 형성된 전극 사이의 간격이 마더 보드에 형성된 전극 간격 보다 더 작은 경우에 적용되는 구조를 띄고 있다. 반도체 칩의 크기가 줄어들면서 칩 전극 사이의 간격 또한 지속적으로 작아지고 있으나 칩이 실장되는 마더 보드 상의 전극 간격은 이를 따르지 못하고 있다. 이러한 문제를 해결하기 위해 칩 바깥쪽에도 패키지 입출력 단자를 배치시킨 것이 팬 아웃 방식의 반도체 패키지다.

그러나 통상의 팬 아웃 방식 반도체 패키지의 경우, 마더 보드의 전극과 칩 전극을 서로 연결하기 위해 인쇄회로기판(PCB)이 포함되며, 칩은 PCB 상에 와이어나 범프(bump)를 통해 실장되므로 제조 공정이 복잡하고 패키지 두께가 두껍다는 단점이 있었다.

FOWLP 기술은 그간 후공정에서 칩 배선에 필수적으로 사용돼 온 PCB를 사용하지 않고 칩과 칩 바깥 영역의 입출력 단자를 상호 연결시키기 때문에 반도체 패키지가 얇아지고 배선길이가 짧아지고 방열 기능이 향상되며 신호 전송도 효율적으로 이뤄지게 되는 장점이 있다.

이렇듯 FOWLP는 칩과 마더 보드 전극의 연결이 PCB가 아니라 폴리머 층과 도전층의 적층으로 이루어진 얇은 재배선층(RDL)을 통해 이루어진다. 재배선층은 두께(수십 μm)가 PCB(수백 μm) 보다 얇으며, 패키지 형성시 전극 위에 직접 형성된다.

그 결과 별개의 공정에서 미리 제조된 PCB에 칩을 연결하기 위한 와이어나 범프가 필요없으므로 FOWLP의 두께를 기존 패키지(0.8~1.0mm)의 절반 수준(0.4~0.6mm)으로까지 줄일 수 있으며, 기존 패키지 공정 대비 원가 경쟁력도 높다. 또한, 얇아진 두께에 의해 방열 기능이 향상되며 배선 길이가 짧아짐에 따라 신호 전송도 효율적으로 이루어진다.

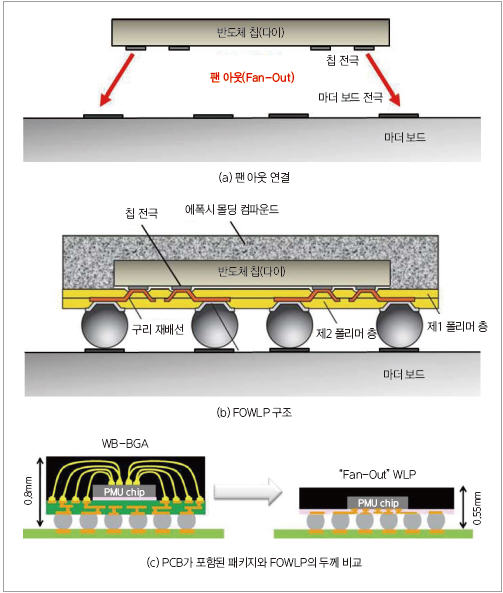

▲ 그림 2. FOWLP 원리 (자료: infineon)

FOWLP의 구체적인 공정을 크게 8가지로 이뤄진다.

첫 번째 단계는 웨이퍼를 절단(Singulation)한다. 두 번째 단계에서는 웨이퍼를 재구성하기에 앞서 글라스 캐리어(Carrier) 위에 구리 기둥(Copper Pillar)을 세운다. 구리 기둥을 세우는 이유는 DRAM을 PoP로 적층할 때 통로 역할을 하고, 에폭시(Epoxy) 몰딩 소재의 휨 현상을 예방하기 위함이다.

세 번째 단계는 굿 (Die)를 캐리어(Carrier)에 뒤집어서 올린다. WLP라고 해서 웨이퍼에 직접 작업하는 것이 아니라 글라스 캐리어(Carrier)에 옮겨 재구성한다는 점을 유념해야 한다. 네 번째 단계는 에폭시(Epoxy) 소재로 웨이퍼를 몰딩한다. 웨이퍼 후면을 평탄화한다.

다섯 번째 단계에서는 이 때 다이(Die)별 개별 몰딩이 아니라 배어 다이(Bare Die)를 일정 간격으로 배열한 후 웨이퍼 형태로 몰딩한다. 여섯 번째 단계에서 캐리어(Carrier)를 제거한다. 일곱 번째 단계는 재배선 패터닝을 하고, 볼(Ball)을 부착한다. 마지막으로 여덟 번째 단계에서 최종 절단한다.

▲ 그림 3. FOWLP와 BGA 원가 구조 비교 (자료: Yole)

일부 업체, FOWLP 기술 우위

그렇다면, 국내 FOWLP 업체의 기술 수준은 어떨까? 한 국내 FOWLP 업체의 경우, EGP 및 Via Frame이라는 특허를 이용해 방열, 접지, 휨 관리 측면에서 해외 경쟁사보다 기술 우위에 있다. 열 특성의 경우, EGP를 적용해 열이 빠져나가는 문을 2개 더 만들었고 이를 통해 방열 효율성이 약 22.5% 증가했다.

접지의 경우, Electrical Path를 최소화해 전기적 특성을 높였다. 한편, FO 공정을 통해 웨이퍼를 얇게 갈게 되는데, 이때 국내 업체의 경우 해외 경쟁사 대비 두께가 60~65% 수준(약 250um)으로 얇다는 점 또한 큰 장점이다. 또한 국내 기업의 경우 멀티칩을 통한 확장성이 용이해 SIP로의 발전이 이뤄지고 있는데 반해, 해외 경쟁사의 경우 싱글칩 형태의 FOWLP를 제공하고 있다는 점 역시 기술 우위를 드러내는 포인트다.

▲ 그림 4. FOWLP와 경쟁 패키지 사이즈 비교 (자료: Yole)

김진희 기자 (eled@hellot.net)