[첨단 헬로티]

FPGA 애플리케이션을 위한 우수한 전력 관리 솔루션을 설계하는 일은 사소한 작업이 아니기 때문에 이와 관련한 많은 기술적인 논의들이 있어 왔다. 이러한 작업의 한 가지 측면은 올바른 솔루션을 찾고 가장 적합한 전력 관리 제품을 찾는 데 있으며, 또 다른 측면은 FPGA에 사용하기 위한 실제 솔루션을 최적화하는 방법을 포함한다.

알맞은 전원 솔루션 찾기

FPGA에 최상의 전원을 공급하는 가능한 솔루션을 찾는 것은 간단하지 않다. 많은 업체들이 FPGA 전원 공급에 적합한 특정 제품들을 시장에 출시하고 있다. FPGA 전원 공급에 특정한 dc-dc 컨버터의 선택에는 어떤 것이 있을까? 많지 않다. 일반적으로 모든 전력 컨버터는 FPGA 전원 공급에 사용할 수 있다.

특정 제품에 대한 권고는 보통 많은 FPGA 애플리케이션에서 FPGA 코어, I/O, 그리고 추가로 DDR 메모리 터미네이션을 위한 레일을 포함해 여러 개의 전압 레일을 필요로 한다는 사실에 기초한다. 종종 여러 개의 dc-dc 컨버터를 하나의 단일 레귤레이터 칩에 모두 통합한 전력관리 IC(PMIC)가 선호된다.

특정 FPGA에 전원을 공급하는 좋은 솔루션을 찾는 한 가지 일반적인 방법은 많은 FPGA 업체가 제공하고 있는 기존에 존재하는 전력 관리 레퍼런스 디자인을 사용하는 것이다. 이 방법은 최적화된 설계를 위한 괜찮은 출발점이다. 하지만 보통 FPGA를 탑재하는 시스템은 전력을 공급 받아야 하는 추가적인 전압 레일과 부하를 필요로 하기 때문에 이러한 설계를 수정해야 하는 경우가 많다. 레퍼런스 디자인에 추가해야 할 필요도 발생한다. 또 다른 고려해야 할 사항은 FPGA의 입력 전력이 고정되어 있지 않다는 점이다. 입력 전압은 FPGA가 구현되는 실제 로직 레벨과 설계에 따라 많이 달라진다. 전력 관리 레퍼런스 디자인의 수정을 마치면, 레퍼런스 디자인의 처음 제안과는 여러 모로 다른 설계가 된다. 따라서 어떤 사람들은 전력 관리 레퍼런스 디자인을 가지고 애쓰지 말고 아날로그디바이스의 LTpowerCAD와 같은 전력 관리 선택 및 최적화 툴에 필요한 전압 레일과 전류를 직접 입력하는 것이 가장 좋은 솔루션이라고 주장한다.

▲ 그림 1. FPG A 전원 공급에 적합한 dc-dc 컨버터를 선택할 수 있는

LTpowerCAD 툴

LTpowerCAD는 개별적인 전압 레일을 위한 전원 솔루션을 생성하는 데 사용할 수 있다. 또한 여러 레퍼런스 디자인이 포함되어 있어 설계자에게 좋은 출발점이 될 수 있다. LTpowerCAD는 아날로그디바이스 웹사이트에서 무료로 다운로드할 수 있다.

전력 아키텍처와 개별적인 전압 컨버터의 선택을 마치면 적합한 수동 부품을 선택하고 전원을 설계해야 한다. 이를 수행할 때에는 FPGA의 특수한 부하 요구사항을 염두에 두어야 한다.

고려해야 하는 사항들

▷개별적인 전류 요구사항

▷전압 레일 시퀀싱

▷전압 레일의 일정한 상승

▷빠른 전력 과도 응답

▷전압 정확도

개별적인 전류 요구사항

모든 FPGA의 실제 전류 소비는 사용 사례에 따라 크게 달라진다. 서로 다른 클록킹 및 다른 FPGA 사양은 다른 전력량을 필요로 한다. 이 때문에 일반적인 FPGA 설계에 대한 최종적인 전원 규격은 FPGA 시스템 설계 과정 동안 변경될 수밖에 없다. FPGA 제조업체는 솔루션이 필요로 하는 특정 전력 레벨을 계산하도록 도와주는 전력 추정 툴을 제공하고 있다. 이러한 정보는 실제 하드웨어를 제작하기 전에 매우 유용하게 활용될 수 있다. 하지만 여전히 이러한 전력 추정 툴로 의미 있는 결과를 얻기 위해서는 FPGA의 설계가 최종적이거나 최소한 최종적인 상태에 가까워야 한다.

엔지니어들은 종종 최대 FPGA 전류를 염두에 두고 전원을 설계한다. 그런 다음, 실제 FPGA 설계가 더 적은 전력을 필요로 한다고 판명되면, 전원의 크기를 감소시킨다.

전압 레일 시퀀싱

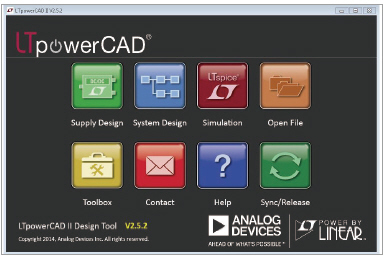

많은 FPGA는 특정한 시퀀스로 상승하면서 작동하기 위해 다른 전원 전압 레일을 필요로 한다. 종종 코어 전압은 I/O 전압이 상승하기 전에 전력을 공급받아야 한다. 그렇지 않으면 일부 FPGA가 손상될 수 있다. 이를 방지하려면 전원을 올바른 순서로 시퀀싱 해야 한다. 간단한 업 시퀀싱은 표준 dc-dc 컨버터에서 인에이블 핀을 사용하여 손쉽게 수행할 수 있다. 그러나 제어되는 다운 시퀀싱 역시 항상 필요하다. 인에이블 핀 시퀀싱만 수행할 경우 좋은 결과를 얻기 어렵다. 보다 나은 해결책은 ADP5014와 같은 향상된 통합 시퀀싱 기능을 갖춘 PMIC를 사용하는 것이다. 조정 가능한 업 및 역 순서의 다운 시퀀싱을 구현하는 특수한 회로 블록은 그림 2에 빨간색으로 표시된다.

▲ 그림 2. 유연한 업 및 다운 시퀀싱을 지원하는 ADP5014 PMIC

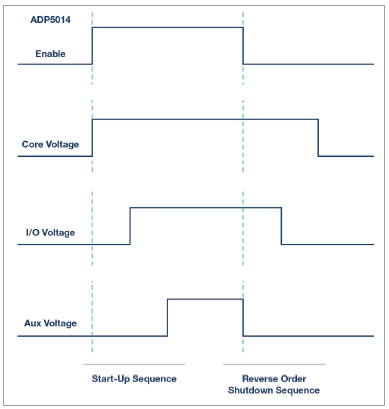

그림 3은 이 디바이스를 사용하여 수행된 시퀀싱을 보여준다. 업 및 다운 시퀀싱을 위한 시간 지연은 ADP5014의 지연(DL) 핀을 사용하여 쉽게 조정할 수 있다.

▲ 그림 3. 여러 FPGA 전원 전압의 스타트업 및 셧다운 시퀀싱

개별적인 전원을 사용한다면, 필요한 온/오프 시퀀싱을 추가적인 시퀀싱 칩이 담당할 수 있다. 일례로 LTC2924가 있다. 이 디바이스는 dc-dc 컨버터의 인에이블 핀이 전원을 켜고 끄도록 제어하거나 또는 하이사이드 N 채널 MOSFET을 구동하여 FPGA를 특정 전압 레일로 연결하고 분리할 수 있다.

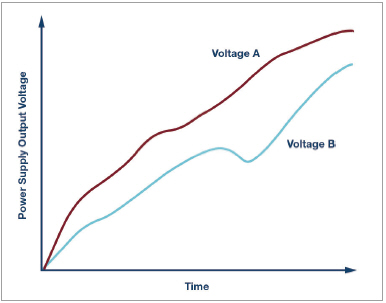

전압 레일의 일정한 상승

전압 시퀀싱 외에도 스타트업 동안 전압의 일정한 상승 역시 필요하다. 이것은 전압이 선형적으로 증가한다는 것을 의미한다(그림 4의 전압 A). 이 그림에서 전압 B는 일정하게 상승하지 않는 전압의 예를 보여준다. 이러한 현상은 스타트업 동안 부하가 특정 전압 레벨에서 많은 전류를 끌어오기 시작할 때 발생할 수 있다. 이를 방지하기 위한 한 가지 방법은 전원에서 더 긴 소프트 스타트를 허용하고, 높은 전류량을 빠르게 공급할 수 있는 전력 컨버터를 선택하는 것이다.

▲ 그림 4. 일정하게 상승하는 전압 A와 일정하게 상승하지 않는 전압 B

빠른 전력 과도 응답

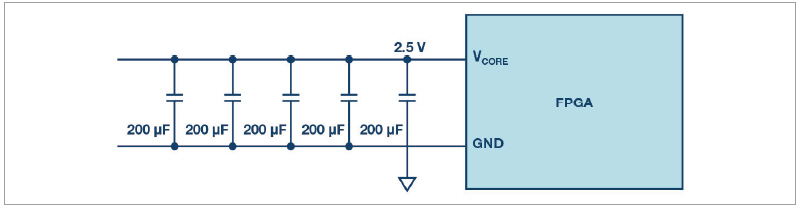

또 다른 FPGA의 특성 중 하나는 FPGA가 매우 빠르게 높은 전류를 소비하기 시작한다는 점이다. 이로 인해 전원에서 높은 부하 과도 현상이 발생한다. 이러한 이유로 많은 FPGA에는 광범위한 입력 전압 디커플링이 필요하다. 세라믹 커패시터가 디바이스의 VCORE와 GND 핀 사이에 매우 가깝게 배치된다. 최대 1 mF 값이 많이 사용된다. 이와 같은 높은 정전용량은 전원에 대한 수요를 낮춰 매우 높은 피크 전류를 공급하도록 도와준다. 하지만 많은 스위칭 레귤레이터와 LDO는 최대 출력 정전용량을 지정하고 있기 때문에 FPGA의 입력 정전용량 요구사항이 전원의 허용되는 최대 출력 정전용량을 초과할 수 있다.

▲ 그림 5. 많은 FPGA의 입력 커패시터 요구사항

전원은 큰 출력 커패시터를 좋아하지 않는다. 스타트업 동안 이러한 커패시터 뱅크는 스위칭 레귤레이터에 출력의 단락 회로처럼 보이기 때문이다. 이 문제에 대한 해결책이 있다. 긴 소프트 스타트 시간은 전원이 단락 회로 전류 제한 모드로 들어가지 않으면서 대형 커패시터 뱅크에서 전압이 안정적으로 상승할 수 있게 한다.

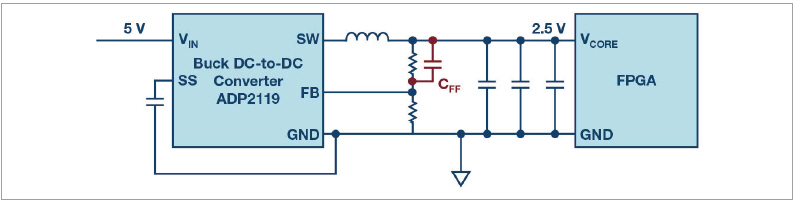

일부 전력 컨버터가 과도한 출력 정전용량을 좋아하지 않는 또 다른 이유는 이러한 정전용량 값이 레귤레이션 루프의 일부가 되기 때문이다. 루프 보상 기능이 있는 컨버터는 레귤레이터의 루프 불안정성을 방지하기 위해 과도한 출력 정전용량을 허용하지 않는다. 그림 6에서 보듯이 피드포워드 커패시턴스를 하이 사이드 피드백 저항에 사용하여 제어 루프에 영향을 미치는 방법이 있다.

▲ 그림 6. 루프 보상 핀이 없는 경우 피드포워드 커패시터를 이용해 제어 루프를 조정할 수 있다.

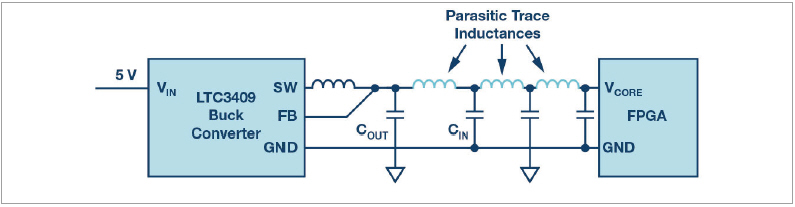

전원의 부하 과도 응답 및 스타트업 동작을 위해 LTpowerCAD와 특히 LTspice를 포함한 개발 툴 체인이 매우 유용하다. 모델링 및 시뮬레이션에 많은 도움이 되는 한 가지 효과는 FPGA의 큰 입력 커패시터를 전원의 출력 커패시터로부터 디커플링 하는 것이다. 그림 6은 이러한 개념을 보여준다. POL(point-of-load) 전원은 부하에 가깝게 배치되는 경향이 있으며, 전원과 FPGA 입력 커패시터 사이에는 일부 PCB 트레이스가 존재하는 경우가 많다. 여러 개의 FPGA 입력 커패시터가 보드에서 서로 옆에 높일 때 일부 저항과 함께 이들 입력 커패시터 사이에 기생 트레이스 인덕턴스가 존재하기 때문에 전원에서 가장 먼 입력 커패시터가 전원의 전달 함수에 더 작은 영향을 갖는다. 모든 커패시터가 보드의 동일한 노드에 연결되는 경우에도 이러한 기생 보드 인덕턴스로 인해 FPGA의 입력 정전용량이 전원의 출력 정전용량의 최대 제한보다 클 수 있다. LTspice에서 기생 트레이스 인덕턴스를 회로도에 추가하여 그러한 효과를 모델링할 수 있다. 적절한 기생 구성요소를 회로 모델링에 포함할 경우 시뮬레이션 결과는 실제에 가깝다.

▲ 그림 7. 전원 출력 커패시터와 FPGA 입력 커패시터 사이의 기생 디커플링

전압 정확도

FPGA 전원의 전압 정확도는 통상 매우 높아야 한다. 단 3%의 변동 허용오차 대역이 매우 일반적이다. 예를 들어 Stratix V 코어 레일인 0.85V를 3%이내 윈도우 전압 정확도로 유지하려면 완전한 허용오차는 단지 25.5mV 대역에 불과하다.

이와 같은 작은 윈도우는 dc 정확도 뿐만 아니라 부하 과도 후 전압 변동을 포함한다. 여기에서도 이와 같은 엄격한 요구사항을 만족하기 위해 전원 설계 과정에서 LTpowerCAD 및 LTspice를 포함한 사용 가능한 전원 툴 체인이 필수적이다.

마지막 제안은 FPGA 입력 커패시터의 선택과 관련된 문제이다. 보통 입력 커패시터가 빠르게 높은 전류를 공급할 수 있도록 세라믹 커패시터가 선택된다. 세라믹 커패시터는 이러한 목적에 잘 맞기는 하지만, 커패시터의 순수한 정전용량 값이 dc 바이어스 전압으로 인해 떨어지지 않는 커패시터를 선택할 필요가 있다.

일부 세라믹 커패시터 중 특히 Y5U 타입은 최대 정격 DC 전압에 가까운 dc 전압으로 바이어스 되면 커패시터의 순수한 정전용량 값이 공칭 액면값의 20%까지 떨어진다.

Frederik Dostal, Analog Device, Inc.