반도체 소자의 정전기 방전(ESD) 테스트 방법에 대해 알아 보기 전에, ESD 제어의 역사를 살펴볼 필요가 있다.

1970년 후반 이전의 반도체 소자는 ESD에 상대적으로 민감하지 않았거나, 정전기방전에 의한 불량 정도가 매우 낮아 주요 관심사가 아니었다.

그 후, LSI 소자가 개발되면서 ESD가 소자 불량의 주요 사항으로 인식되기 시작했고, 1980년대 초반 자동차 업계에서 ESD 통과 레벨을 선정하면서 소자에 대한 ESD 테스트가 실시됐다.

당시 제조 현장 조건은 지금만큼 좋지 않아 인체에 대전되는 정전기 에너지가 1∼2kV까지 만들어지기도 했다. 이에 자동차 업계에서 포드가 MM 200V를, GM과 크라이슬러가 인체 대전 모델(Human Body Model ; HBM)에 집중하면서 HBM 2kV를 소자의 ESD 통과 레벨로 사용하게 됐다.

이 일을 계기로 경쟁 체제였던 대부분의 소자 업체에서는 묵시적인 산업 표준(De Facto Target)으로 HBM 2kV를 사용하게 됐고, 대부분의 소자는 최근까지 이 수준에 이르도록 보호 회로 설계를 실행하게 됐다.

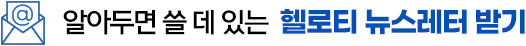

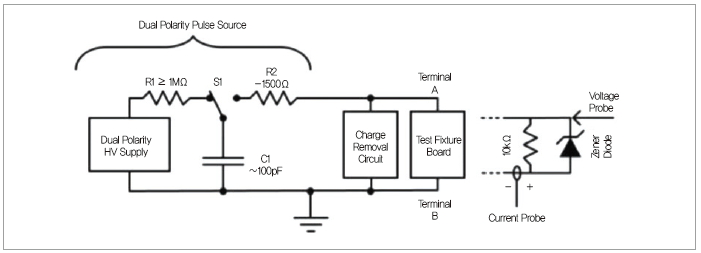

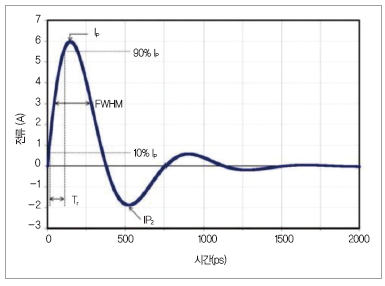

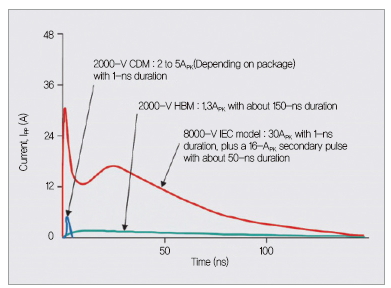

그림 1. 대표적인 HBM 파형

인체 대전 모델

예전 HBM 테스트의 표준은 사실, 여러 단체에서 약간씩 다른 형태의 테스트 방법으로 존재했다. 대부분의 소자 업체에서 사용하던 표준은 미국 JEDEC 표준으로 JESD22-114 버전 문서였다. 그 외 다른 문서로는 ANSI/ESD S5.1 표준으로 JEDEC과 테스트 방법이 약간 상이했다.

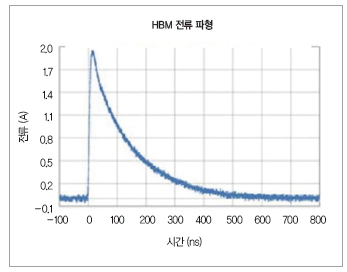

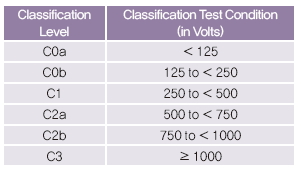

표 1. ANSI/ESD/JEDEC HBM ESD 소자 등급 레벨

그 후 2009년부터 JEDEC과 ESD Association에서 공동으로 Joint Working Group을 만들어 두 기관의 합의된 표준 문서인 ANSI/ESD/JEDEC JS-001-2010을 만들게 됐고, 지금은 2014년에 발간된 ANSI/ESD/JEDEC JS-001-2014가 최종 문서로 사용되고 있다.

그림 2. HBM ESD 회로

최종 업데이트된 HBM 테스트 회로 블록 다이어그램(Circuit Block Diagram)은 그림 2와 같으며, 테스트 원리는 100pF의 인체 정전 용량을 가진 전원 소스에서 1.5kΩ을 가진 스위치를 통해 소자로 펄스가 들어가도록 구현한 것이다. 이때 펄스는 낮은 전압 125V부터 인가하며, +/- 펄스를 교대로 인가해야 한다.

이전에는 각 수준의 펄스를 3차례 인가했다면, 2014년 버전에서는 한 번만 인가하도록 내용이 업데이트됐다. 또한 그림 2에 나타난 바와 같이, 회로 구성에서 소자 이외의 부분에 잔류하는 에너지가 다음 방전에 영향을 주지 않도록 이전 방전에 의한 잔류 에너지를 제거하는 회로를 구성하도록 변경된 부분이 있다.

그림 3. 대표적인 CDM 파형

기타 자세한 내용은 표준 전문(ANSI/ESD/JEDEC JS-001-2014 ESDA/JEDEC Joint Standard for Electrostatic Discharge Sensitivity Testing-HBM-Component Level)을 참조하기 바란다.

대전 소자 모델

대전소자모델(Charge Device Model ; CDM)은 1970년대 말 AT&T 벨 연구소에서 처음 발견한 모델이다. 이후 HBM에 비해 표준 개발이 상대적으로 늦어진 점, 발견 당시보다 반도체 공정의 미세화와 자동화 공정이 확산된 점 등에 의해 최근 ESD 불량의 주요 원인으로 떠오르면서 중요성이 부각되고 있다.

초기의 반도체 소자는 소자 패키지가 작고, 단순하며 핀 수가 적었다. 이러한 이유로 핀 조합(Pin Combination) 테스트를 수행하는 HBM의 경우 복잡성이 낮고 상대적으로 회로 개선이 용이했다.

그러나, CDM의 경우는 반도체 소자 코어 로직의 산화물(Oxide) 혹은 접합(Junction) 불량을 일으키는 형태이며 IO 핀 주변에서 발생하던 HBM과는 불량의 위치, 형태 등이 많이 다르다.

자동차 업계를 중심으로 형성됐던 ESD HBM 통과 레벨의 경우와 같이, 산업계에서는 CDM 부품의 ESD 통과 레벨로 500V가 널리 사용됐다. 상대적으로 수준이 낮은 이유는 방전 시간이 상대적으로 짧아 더 많은 에너지가 방전에 사용되면서 관리 가능한 수준의 방전에너지가 상대적으로 낮기 때문이다.

CDM 방전의 경우 최대 전류(Peak Current)를 형성하는 주 요인은 디바이스 패키지의 크기에 의해 달라진다. 따라서, 패키지가 큰 BGA, LGA 등과 같은 소자의 CDM 방전 전류 에너지는 다른 작은 패키지 소자에 비해 크며, 불량의 형태도 훨씬 심각할 수 있다.

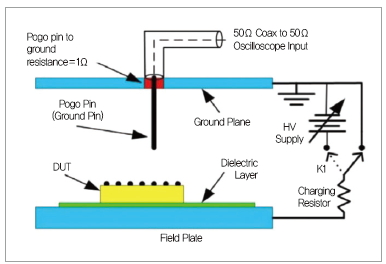

그림 4. 필드 유도 CDM 테스트 다이어그램

CDM 테스트는 그림 4와 같이 절연된 소자 IO 핀이 데드버그(Dead Bug) 형태로 하늘을 향하게 하고, 하부에 전압이 인가되는 전계 판으로부터 유도되는 전계가 소자에 영향을 주도록 하며, 이때 접지에 연결된 포고 핀(Pogo Pin)을 통해 대전된 소자의 IO 핀을 터치해 방전이 발생하도록 하는 방식이다. 이 방식은 HBM 방식과 전혀 다르며, CDM과의 유사성이나 상관관계도 갖고 있지 않다.

표 2. ANSI/ESD/JEDEC CDM ESDS 디바이스 분류 레벨

이러한 CDM 방전은 실제 현장에서 발생하는 ESD 불량의 많은 부분에 직접적인 연관성을 갖고 있을 수 있으므로, 대부분의 기업에서는 CDM 관련 스펙을 확인하고 신중하게 테스트해야 한다.

CDM 테스트의 중요한 특징 중 하나는 상승 시간(Rise Time)이 다른 방전에 비해서 빠르기 때문에(250∼450ps 미만을 기준으로 했을 때), 적절한 스피드의 오실로스코프와 전류 프로브(Current Probe) 등을 세밀하게 준비해 둘 필요가 있다는 점이다.

자세한 사항은 해당 문서(ANSI/ESD/JEDEC-JS-002-2014 ESDA/JEDEC Join Standard for Electrostatic Discharge Sensitivity Testing-CDM-Component)를 참조하기 바란다.

시스템/세트 수준

아마도, 이 부분이 산업계에서 가장 많은 오해를 불러 일으키고 있는 것 같다. 필자가 구글에서 ESD HBM Tester로 조회하고 이미지 검색을 실시해 보니, 수많은 System Level Waveform 이미지가 HBM 검색을 통해 확인됐다. 아마도 이러한 부분이 처음 ESD를 접하는 엔지니어들에게 많은 오해를 불러 일으키는 것 같다.

앞서 설명한 두 가지 모델, HBM과 CDM은 모두 소자(Component)를 대상으로 Unpower, 즉 전압을 인가하지 않고 수행하는 테스트이고, 제조 공정 중 반도체 소자가 정전기로 인해 파괴될 수 있는 수준은 어느 정도인지 파악하기 위해 만들어진 표준이다.

그림 5. HBM, CDM & 시스템 ESD 파형

이에 비해, 시스템/세트 수준(System Level) 테스트는 정상적인 전압을 인가한 파워 온(Power On) 테스트이며, 반도체 소자를 포함하여 완성된 전체 시스템(예를 들면 노트북 컴퓨터, 데스크톱 컴퓨터, LCD 모니터, 완성된 자동차 등)에 펄스 스트레스를 가한다.

이때는 소자 불량이 아니라 전체 시트템의 오동작이나 리셋, 전원 리부팅 등과 같은 일이 발생하는가를 모니터링하는 개념의, 전혀 다른 수준의 테스트 결과를 기대하게 된다. 그래서 소자 수준이 아닌, 시스템 수준의 ESD 테스트라고 구분해서 말한다.

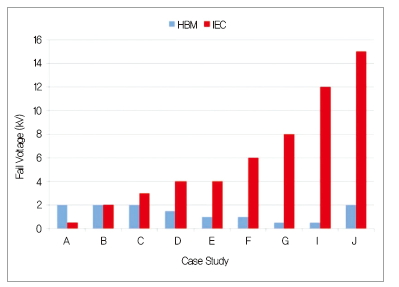

그림 6. HBM 견고성은 시스템 수준의 ESD와 관계 없다

그렇다면 사람들이 이 부분의 테스트에서 혼동하는 이유는 무엇일까. 그것은 전통적으로 많은 이들에게 정전기 방전이 HBM으로 인식돼 왔기 때문일 수도 있고, 시스템 수준 테스트를 설명하는 도중에 언급되는 인체(Human Body) 때문일 수도 있다. 시스템 수준 테스트의 개념은 보행이나 움직임으로 인해 대전된 인체가 드라이버 등의 공구를 손에 쥐고 완성된 시스템의 도체 혹은 부도체 부분에 접촉하는 순간 발생하는 정전기 방전을 형상화한 모델이다. 이 부분 때문에 많은 혼선이 야기되는 것 같다.

그러나, 대부분의 경우 소자 수준 HBM의 ESD 민감도와 시스템 수준 ESD 테스트 사이에는 서로 상관 관계가 없다는 것이 수십억 개 소자의 현장 경험을 통해 입증됐다. 대부분의 세트 업체에서는 아직도 현장에서 발생하는 ESD 불량 해결 방법을 제조 현장에서 찾지 않고, 소자 설계 개선을 통해 구현할 수 있다고 생각하며 시스템 수준 테스트 결과를 근거로 하여 소자 문제로 귀결하고 있다. 사실, 시스템 문제는 시스템 설계에서 해결해야 하고, 소자 문제는 소자에서 해결해야 한다.

시스템 수준 테스트의 경우 크게 두 가지로 나눠 실시된다. 접촉(Contact Discharge) 방식과 비접촉(Air Discharge) 방식이다. 접촉 방식 테스트의 경우, 사용자가 쉽게 접촉할 수 있는 IO 포트와 시스템의 도체 부분에 접촉해 실시하며, 모든 방전은 수직으로 실시한다. 그리고 비접촉 방식 테스트의 경우, 스위치나 키보드 등 사용자 접촉 부위의 부도체 재료에 대해 실시하며 모든 방전은 표면에서 수직으로 실시한다. 수직으로 실시하지 않을 경우 반복성이 결여되는 테스트 결과가 나을 수 있으며, 그 결과에 대한 신뢰성에 문제가 제기될 수 있다.

자세한 내용은 해당 문서(IEC 61000-4-2:2008 Electromagnetic Compatibility(EMC)-Part 4-2: Testing and Measurement Techniques-Electrostatic Discharge Immunity Test)를 참조하기 바란다.

유용훈 대표 _ 국제정전기협회 한국지부 /코어인사이트(주)