전원관리 집적회로(PMIC)는 개별 공급 전압에서 유연성과 프로그램 가능성을 통해 멀티 프로세서 및 FPGA를 구동할 수 있다. 따라서 공격적인 동적 전압 스케일링(Dynamic Voltage Scaling ; DVS) 환경에서도 효율적으로 전원을 관리할 수 있다.

PMIC(Power-Management Integrated Circuit)는 비용 효과적인 전원 공급 장치 솔루션으로, 멀티 전원 공급 장치 레일을 필요로 하는 애플리케이션에 적합하다. PMIC는 프로세서 및 FPGA, 주변장치 전원 등 시스템 레벨 전원에 주로 사용된다. 대표적인 애플리케이션은 개인용 전자 기기, 산업용 디바이스, 오토모티브 디바이스 등 매우 많다.

PMIC는 일반적으로 멀티 공급 장치 레일로 구동되는 벅/부스트 컨버터, 벅 컨트롤러, 저드롭아웃 레귤레이터 등으로 구성되어 있다. 그리고 PMIC는 멀티 공급 장치 레일을 하나의 IC 안에 결합시키므로 커패시터, 인덕터, 전력 MOSFET과 같은 개별 레귤레이터에 필요한 외부 부품들을 인쇄회로기판(PCB) 설계 및 레이아웃으로 잘 관리해야 한다.

PMIC와 더불어, 특정 바이어스 전력 요건에 가까운 잠재적인 솔루션도 파악해야 한다.

이 글에서 제공하는 샘플 설계 및 리소스는 설계자들이 절연 전원 솔루션으로 시스템을 준비하고 실행하는 데 참조할 수 있다.

일반적으로 배치와 관련해 모든 외부 부품들을 PMIC 근처에 두어야 한다는 오해를 많이 하곤 한다. 그래서 PMIC를 이용한 설계는 특히 원거리 POL(Point-Of-Load) 애플리케이션에 사용되는 고전력 통합형 전원 컨트롤러에서 제한적이며 유연성이 떨어진다고 생각한다. 그러나 실제로 꼭 그런 것은 아니다.

여기서는 외부 부품을 잘 배치하고 원거리 POL 조건에서 비용 효과적인 솔루션을 가능하게 하는 PCB 설계 및 레이아웃 전략에 대해 설명한다.

벅 컨트롤러의 효율을 높여라

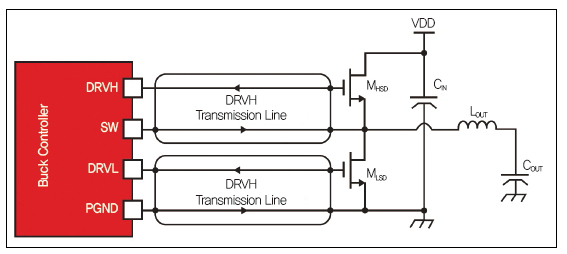

그림 1. 전형적인 벅 컨트롤러 블록 다이어그램과 외부 부품들

그림 1은 전형적인 벅 컨트롤러 블록 다이어그램을 나타낸 것이다. 외부 부품들은 주로 단독 또는 멀티 입력 커패시터(CIN), 단독 또는 멀티 출력 커패시터(COUT), 출력 인덕터(LOUT)로 구성되어 있다.

또한 여기에는 2개의 외부 전력 MOSFET(MHSD 및 MLSD)과 부트스트랩 커패시터(CBOOT)가 하이사이드 드라이버에 필요하다.

벅 컨트롤러는 보통 고성능 애플리케이션을 위해 설계되므로 최적의 효율을 달성하려면 파워 트레인(MHSD, MLSD CIN, LOUT, COUT)을 POL과 가능한 한 가깝게 두는 것이 좋다. 그러나 성능 때문에 컨트롤러 IC를 파워 트레인에 너무 가까이 배치할 필요는 없다. 해당 애플리케이션에 따라서는 특정 레이아웃 전략으로 IC 배치의 제한을 완화시킬 수 있다.

다음에는 외부 부품과 IC의 기능과 배치, 그리고 PCB 레이아웃 전략에 대해 설명한다.

벅 컨트롤러의 파워 트레인에서 고려해야 할 사항

전력 MOSFET, 입력 커패시터, 출력 인덕터, 출력 커패시터가 벅 컨트롤러의 파워 트레인을 구성한다. 입력 커패시터는 로컬 전원 공급 장치 역할을, 출력 인덕터 및 커패시터는 저주파수 필터 기능을 하며, 전력 MOSFET은 스위칭 전력 변환을 수행한다.

이 부품들의 경우, 모두 PCB에서 가깝게 배치해야 믿을 수 있으며 효율적인 성능을 달성할 수 있다. 앞서 언급한 바와 같이, 벅 컨트롤러는 고성능 애플리케이션에 주로 사용된다. 따라서 파워 트레인을 POL 근처에 배치해야 파워 손실을 최소화할 수 있다.

그러나 컨트롤러 IC는 하이사이드 드라이버(DRVH), 로우사이드 드라이버(DRVL), 스위칭(SW) 신호들을 라우팅할 수 있도록 적절한 레이아웃 가이드라인만 지킨다면, 부품들로부터 비교적 멀리 떨어뜨려도 괜찮다.

레이아웃 라우팅 전략

PMIC를 POL에서 어느 정도 떨어뜨려도 되는지는 DRVH 및 DRVL 신호의 라우팅 길이로 결정할 수 있다. 이 2개 신호의 무결성이 유지된다면, 컨트롤러의 성능은 하락하지 않는다. 특히 DRVH 및 DRVL 신호가 하이사이드 드라이브(HSD) FET와 로우사이드 드라이브(LSD) FET를 동시에 켤 만큼 왜곡될 경우, 크로스 컨덕션(Cross-conduction) 때문에 신뢰도 문제나 전원 손실 문제가 발생할 것이다.

DRVH 및 DRVL은 슬루(Slew) 속도가 빠른 고속 게이트 드라이브 신호이기 때문에, 양호한 신호 무결성을 유지하기 위해서는 그 라우팅을 PCB 레이아웃에서 트랜스미션 라인으로 취급해야 한다.

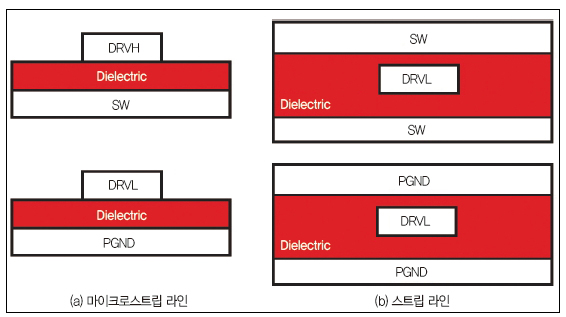

DRVH 및 DRVL의 신호 라우팅을 모델링하면 그림 2와 같다. DRVH 신호의 리턴 경로는 SW 신호이고, DRVL 신호의 리턴 경로는 파워 그라운드(PGND)라는 데 주목하자.

그림 2. 트랜스미션 라인 역할을 하는 하이사이드 드라이브(DRVH)와 로우사이드 드라이브(DRVL)

긴 트랜스미션 라인 라우팅의 경우, 가장 간단하고 비용 효과적인 전략이라면 마이크로스트립 라인 레이아웃 기법이나 스트립 라인 레이아웃 기법을 사용하여 라인 임피던스를 제어하는 것이다.

그림 3. 하이사이드 드라이브(DRVH)와 로우사이드 드라이브(DRVL) PCB 라우팅 단면도

그림 3은 마이크로스트립 라인 및 스트립 라인 라우팅의 PCB 단면도이다. 마이크로스트립 라인 방식은 상위 PCB 레이어에서 신호를 라우팅하는 데 적합하고, 스트립 라인 방식은 PCB 내부 레이어에서 신호를 라우팅하는 데 좋다.

표 1은 마이크로스트립 라인의 전형적인 PCB 기생을 나타낸 것이다.

표 1. 평면으로 모델링된 전형적인 마이크로스트립 라인 기생과 리턴 경로

여기서 언급한 레이아웃 전략의 효과를 증명하기 위해, 3개의 컨트롤러와 3개의 컨버터를 갖고 있는 PMIC, TPS650860을 이용해 전형적인 사례의 시나리오를 시뮬레이션해 보았다. 표 1에 나타난 바와 같이, 추정되는 PCB 기생과 CSD87381P의 파워 FET을 이용한 시뮬레이션에서, 이 PMIC 컨트롤러를 POL로부터 11인치 떨어뜨려 배치할 수 있다는 것을 확인할 수 있었다.

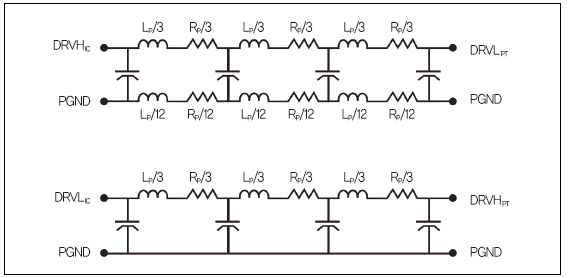

그림 4는 DRVH와 DRVL의 트랜스미션 라인 모델을 묘사한 것이다. 여기서 DRVH 라인보다 SW 영역을 4배 더 넓게 모델링했고, PGND는 저임피던스 그라운드 영역으로 모델링했다.

그림 4. 시뮬레이션에 사용된 트랜스미션 라인 모델

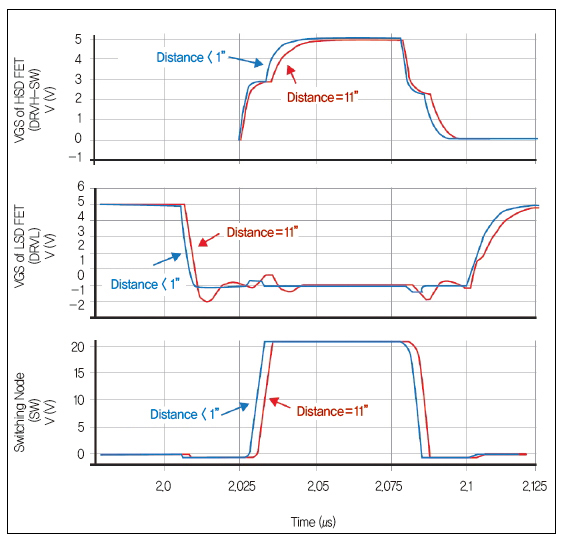

그림 5. 컨트롤러와 파워 트레인 및 POL의 간격이 1인치 미만인 시뮬레이션 결과와 11인치인 시뮬레이션 결과 비교

그림 5의 시뮬레이션 결과는 파워 FET 게이트-소스 전압의 2개 시나리오를 비교한 것이다. 첫 번째 사례에서는 파워 트레인 부품을 PMIC에 매우 가까이 배치했다(1인치 이하). 두 번째 사례에서는 파워 트레인 부품을 POL과 가까이 배치하되 PMIC로부터는 11인치 떨어뜨려 놓았다. 이 시나리오에서는 11인치 마이크로스트립 라인을 이용해 게이트-드라이브 신호를 라우팅했다.

이 시뮬레이션 결과를 살펴보면, 두 번째 시나리오[그림 3(b)]는 첫 번째 시나리오[그림 3(a)]보다 약간 더 많은 나노초 지연을 보인다. 따라서 게이트-드라이브 신호의 라우팅이 매우 짧다. 이와 같은 추가적 지연 타임의 원인은 게이트-드라이브 신호가 트랜스미션 라인을 통해 경험하게 되는 지연 때문이다.

또한 두 번째 시나리오의 HSD 게이트 신호(DRVH-SW) 상승 타임과 하락 타임이 약간 더 높다. 그렇지만 첫 번째 시나리오와 크게 차이가 나는 것은 아니다.

DRVL 신호는 가벼운 오버슛과 언더슛을 갖는다. 이것은 신호가 긴 트랜스미션 라인을 통과할 때 당연히 예상되는 일이다. 이러한 오버슛 레벨은 LSD MOSFET을 켤 만큼 극심하지는 않으므로, 심각한 성능 문제가 생기지는 않는다.

부트스트랩 커패시터에서 고려해야 할 사항

부트스트랩 커패시터의 기능은 DRVH 드라이버에서 부동 로컬 전원 공급 장치 역할을 하는 것이다. 따라서 컨트롤러 IC에 가깝게 배치하는 것이 좋다.

이 부트스트랩 커패시터의 라우팅 저항은 DRVH 신호의 충전 시간에 영향을 준다. 따라서 라우팅 저항을 약 100mΩ으로 유지해야 한다.

그림 6. DRVH 버퍼와 부트스트랩 커패시터 및 PCB 라우팅 기생

그림 6은 기생 라우팅 저항을 나타낸 것이다. 여기서 RPARA는 기생 저항 모델이고, DRVH는 HSD MOSFET을 켤 때 끌어낸 전류이다.

통합형 벅 컨트롤러의 외부 부품들을 모두 PMIC 가까이에 배치할 필요는 없다. 본문에서 파워 트레인 부품은 레이아웃 가이드라인을 지켜 POL 근처에 배치할 수 있다.

통합형 벅 컨트롤러를 갖춘 텍사스 인스트루먼트(TI)의 PMIC로는 TPS65911과 TPS650680이 있다.

컨트롤러를 원거리 POL 애플리케이션의 솔루션으로 활용할 때 PCB 레이아웃의 핵심은 다음과 같다.

•신뢰할 수 있는 최대 성능을 달성하려면 입력 커패시터 및 파워 FET를 서로 가까이 배치한다.

•최대 전원 효율을 달성하려면 인덕터 및 출력 커패시터를 FET과 입력 커패시터에 가깝게 배치한다.

•파워 FET, 인덕터, 입출력 커패시터 등 파워 트레인 부품들을 POL에 배치한다.

•DRVH 및 DRVL 라우팅을 트랜스미션 라인으로 취급한다.

•마이크로스트립 라인 및 스트립 라인 기법이 최고의 성능을 달성한다.

•부트스트랩 커패시터를 PMIC 근처에 배치하여 DRVH의 드라이브 성능을 유지한다.

Sujan Manohar _ TI

Bhaskar Ramachandran _ TI

Puneet Sehgal _ TI

Kae Wong _ TI