아날로그 디자이너는 증폭기 설계 시 안정성을 높이기 위해 노력한다. 그럼에도 불구하고 다양한 유형의 부하로 인해 현장에서 발진을 일으키는 경우가 흔하다. 일례로 피드백 네트워크를 부적절하게 설계하면 발진이 발생할 수 있다. 전원 바이패싱이 불충분한 것 또한 문제가 될 수 있으며, 입력과 출력이 단일 포트 시스템으로서 자체적으로 발진을 일으킬 수 있다. 이 글에서는 발진이 일어나는 주요 원인과 이의 해결책에 대해서 살펴본다.

기본 동작

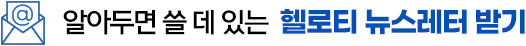

그림 1(a)는 비-레일 투 레일 증폭기의 블록 다이어그램을 나타낸다. 입력이 gm블록을 제어하면 그림에서 나타낸 블록이 이득 노드를 구동하고 출력 시 버퍼링이 이루어진다.

그림 1. 비-레일투레일 연산 증폭기 토폴로지(a), 레일투레일 연산 증폭기 토폴로지(b), 연산 증폭기의 이상적 주파수 응답(c)

보상 커패시터 CC는 지배적 주파수 응답 소자이다. 접지 핀이 있다면 CC가 접지로 리턴될 것이다. 하지만 통상적으로 연산 증폭기는 접지를 이용하지 않으므로 이 커패시터 전류가 전원 중의 어느 한쪽이나 양쪽으로 리턴 될 것이다.

그림 1(b)는 레일 투 레일 출력을 제공하는 증폭기의 블록 다이어그램이다. 입력 gm의 출력 전류가 전류 커플러로 전달되고, 전류 커플러가 구동 전류를 출력 트랜지스터들 간 분할한다. 이때 2개의 CC/2가 주파수 응답에 있어서 지배적이며 실제적으로 병렬을 이룬다.

이 두 토폴로지를 사용하면 외부 피드백을 사용하는 거의 대다수 연산 증폭기를 설명할 수 있다.

그림 1(c)는 이들 이상적 증폭기의 주파수 응답을 보여주는 것으로서, 이들 증폭기는 전기적으로는 다르지만 비슷한 동작을 나타낸다. gm과 CC가 구현하는 단일 극점 보상은 단위-이득-대역폭 곱 주파수, 즉 GBF = gm/(2πCC)를 제공한다. GBF/AVOL부근에서 이들 증폭기의 위상 지연(phase lag)이 -180°에서 -270°로 떨어진다.

AVOL은 개방 루프 증폭기 DC 이득이다. 이 주파수는 지난 주파수들에서 -270°로 위상이 유지된다. 이를 우성 극점 보상(dominant pole compensation)이라고 한다. 이때 CC극점이 응답에 있어서 지배적이며 능동 회로의 다양한 주파수 한계를 은폐시킨다.

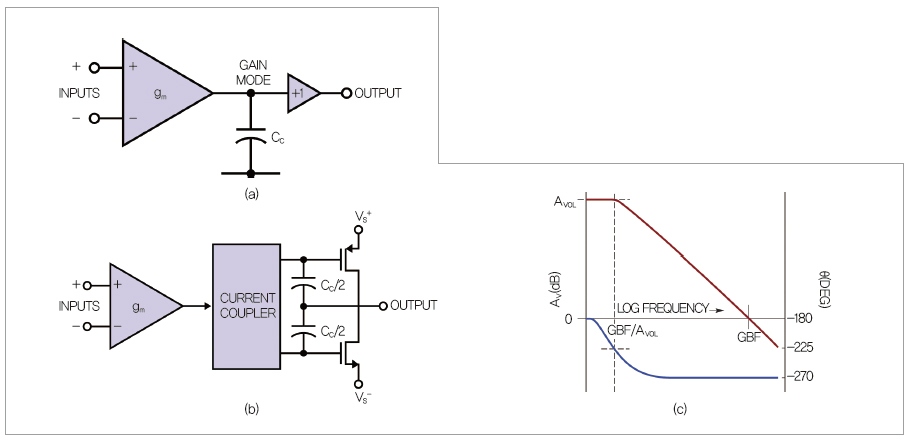

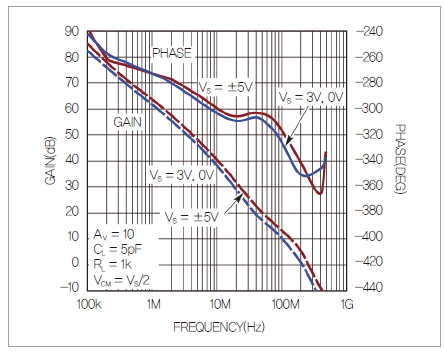

그림 2는 LTC6268 증폭기의 주파수에 따른 개방 루프 이득 및 위상 응답을 보여준다. 이 IC는 레일투레일 출력과 3fA 바이어스 전류를 특징으로 하는 간소하고 소형화된 저잡음 500MHz 증폭기로서, 실제 증폭기 동작을 살펴보기에 좋은 예다.

그림 2. LTC6268의 주파수에 따른 이득 및 위상

약 0.1MHz 부근에서 우성 보상(dominant compensation)의 -90° 위상 지연이 시작되고, 8MHz 부근에서 -270°를 지나며, 30MHz를 넘어서는 -270° 너머까지로 변화한다.

실제적으로 모든 증폭기가 기본적인 우성 보상 지연에 더해서 추가적 이득 스테이지와 출력 스테이지로 인한 추가적인 고주파 위상 지연을 갖는다. 통상적으로 추가적 위상 지연은 GBF/10 부근에서 시작된다.

피드백을 사용할 때의 안정성은 루프 이득과 위상에 크게 관련되어 있다. 다시 말해서 AVOL과 피드백 계수를 곱한 것, 즉 루프 이득에 관한 문제이다. 리니어의 LTC6268을 단위 이득 구성으로 연결하면, 출력 전압의 100퍼센트가 피드백 된다.

극히 낮은 주파수일 때는 출력이 -입력의 부(negative), 즉 -180° 위상 지연이 된다. 보상이 증폭기를 통해 -90° 지연을 추가함으로써, -입력에서 출력까지 지연이 -270°가 된다. 루프 위상 지연이 ±360° 또는 이의 배수가 되고 루프 이득이 최소한 1V/V이 된다.

다시 말해서 0dB이 되었을 때 발진이 발생한다. 위상 마진은 이득이 1V/V, 즉 0dB일 때 위상 지연이 360°로부터 얼마나 멀리 떨어져 있는가를 나타내는 것이다. 그림 2에서는 위상 마진이 130MHz일 때 약 70°라는 것을 알 수 있다(10pF 빨간색 곡선). 이 정도이면 아주 우수한 수치이다. 대략 35°까지의 위상 마진을 사용할 수 있다.

이득 마진(gain margin)은 많이 논의되고 있지 않으나, 이 역시 중요한 파라미터이다. 어느 지점의 높은 주파수에 이르러서 위상이 제로 마진으로 감소하면 이득이 최소한 1V/V로, 즉 0dB가 되었을 때 증폭기가 발진을 일으킬 것이다. 그림 2에서 보듯이 위상이 0으로 떨어지는 때는(또는 360°의 배수, 또는 이 그림에서처럼 -180°) 1GHz일 때 이득이 약 -24dB을 나타낸다. 이는 매우 낮은 이득이다. 그러므로 이 주파수일 때는 발진이 일어날 수 없다. 실제적으로 이득 마진은 최소한 4dB가 되어야 한다.

역보상 증폭기

LTC6268은 단위 이득으로 안정적으로 설계되어 있다. 하지만 연산 증폭기 중 몇몇은 의도적으로 그렇지 않도록 설계되어 있다. 증폭기 보상을 높은 폐쇄 루프 이득에 대해서만 안정적으로 설계하면 단위 이득 보상보다 더 높은 슬루율(slew rate), 더 넓은 GBF 및 더 낮은 입력 잡음을 확보하는 것이 가능하다.

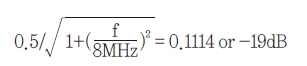

그림 3은 LT6230-10의 개방 루프 이득 및 위상을 보여준다. 이 증폭기는 10 이상의 피드백 이득으로 이용하도록 설계된 것으로서, 피드백 네트워크가 최소한 10의 계수로 출력을 감쇠한다. 이 피드백 네트워크를 사용하면 개방 루프 이득이 10V/V, 즉 20dB이며 50MHz 주파수에서 위상 마진이 58°이다(단, ±5V 전원 사용 조건). 단위 이득일 때는 위상 마진이 대략 0°에 불과하고, 그러면 증폭기가 발진을 일으킬 것이다.

그림 3. LT6230-10의 주파수에 따른 이득 및 위상

여기서 한 가지 알 수 있는 것은, 모든 증폭기가 최소한으로 안정적인 이득보다 더 높은 폐쇄 루프 이득을 제공함으로써 훨씬 더 안정적일 수 있다는 것이다. 이득이 1.5만 되더라도 단위 이득 안정적 증폭기보다 훨씬 더 안정적일 수 있다.

피드백 네트워크

피드백 네트워크 자체로 인해 발진을 일으킬 수도 있다.

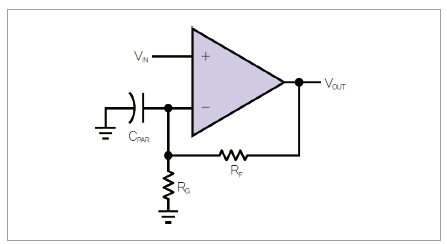

그림 4에서는 피드백 분할기와 병렬로 기생 커패시턴스를 나타내고 있다. 회로 보드 내에서 개별 소자 각각의 단자는 접지에 대해서 약 0.5pF의 커패시턴스를 갖는다.

그림 4. 기생 커패시턴스로 인한 피드백 네트워크 로드

또한 노드들의 최소 커패시턴스는 2pF이고, 트레이스는 인치당 ∼2pF에 이른다. 그러므로 손쉽게 기생 성분이 5pF에 달할 수 있다.

예를 들어 LTC6268의 이득이 +2라고 하자. 전력을 절약하고자 RF와 RG의 값을 꽤 높은 10kW으로 설정한다. CPAR = 4pF이면 피드백 네트워크는 1/(2·RF||RG·CPAR), 즉 8MHz에서 극점을 갖는다.

피드백 네트워크의 위상 지연이 -atan(f/8MHz)인 점을 활용해 루프가 360° 지연이 되는 지점이 약 35MHz라는 것을 계산할 수 있다. 이때 증폭기 지연이 -261°이고 피드백 네트워크 지연이 -79°이다. 이 위상 및 주파수이면 증폭기의 이득이 여전히 22dB이다. 또한 분할기 이득은 다음과 같다.

증폭기의 22dB와 피드백의 -19dB를 곱하면 루프 이득은 +3dB에 0° 위상이다. 그러므로 회로가 발진을 일으킨다.

따라서 기생 커패시턴스를 이용해서 작동할 수 있도록 피드백 저항 값을 낮추어야 하며, 결국 피드백 극점이 루프의 단위 이득 주파수보다 훨씬 높도록 해야 한다. 극점 대 GBF 비율이 최소한 6배가 되어야 한다.

연산 증폭기 입력 자체가 CPAR을 따라 상당히 큰 캐패시턴스를 가질 수 있다. 특히 잡음이 낮고 VOS가 낮은 증폭기는 대형 입력 트랜지스터를 내장하고 있으며 피드백 네트워크를 받을 때 여타의 증폭기보다 더 큰 입력 캐패시턴스를 가질 수 있다. CPAR과 병렬로 얼마만큼의 커패시턴스가 있을 수 있는지에 대해서는 데이터 시트에서 확인할 수 있다.

다행히 LTC6268은 이 커패시턴스가 단 0.45pF 밖에 되지 않아, 저잡음 증폭기로서는 상당히 낮다.

Linear Technology에서 무료로 제공하는 LTspice®프로그램으로 매크로 모델을 사용해서 기생 성분을 포함하는 회로를 시뮬레이트 할 수 있다.

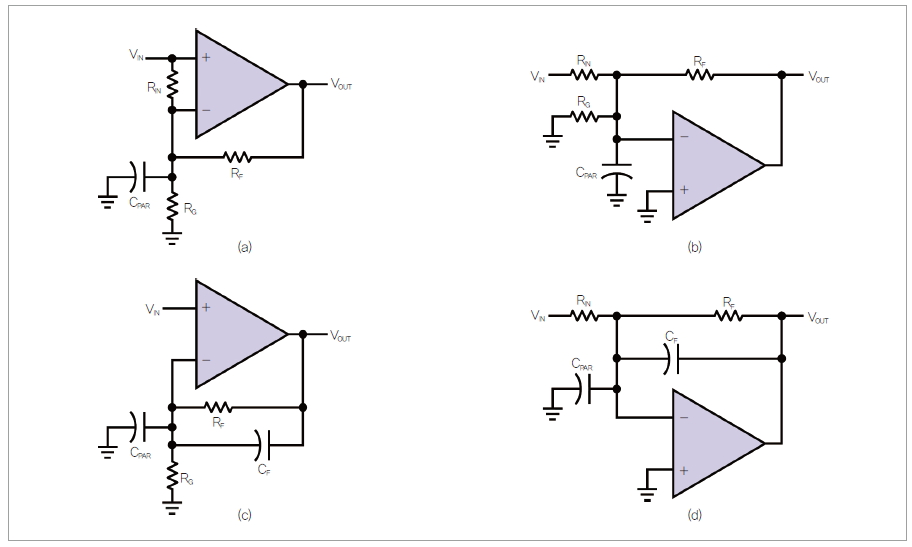

그림 5에 분할기가 커패시턴스를 더 잘 허용할 수 있게 하기 위한 기법들을 나타냈다. 이 중 그림 5(a)는 비반전 증폭기 구성에 RIN을 추가한 것이다.

그림 5. CPAR 효과를 낮추기 위한 기법들

VIN이 낮은 임피던스(<< RIN)이면, RIN이 폐쇄 루프 이득은 변화시키지 않으면서 피드백 신호를 감쇠시킨다. 또한 RIN은 또한 분할기 임피던스를 낮춤으로써 GBF 이상으로 피드백 극점 주파수를 높일 수 있다. 하지만 RIN에 의해서 루프 대역폭이 감소하고 입력 오프셋과 잡음이 커진다.

그림 5(b)는 비반전 구성이다. 이 또한 RG가 폐쇄 루프 이득을 변화시키지 않으면서 루프를 감쇠한다. 이 경우에는 RG에 의해서 입력 임피던스는 방해를 받지 않으나 잡음, 오프셋 및 대역폭이 악화된다.

그림 5(c)는 비반전 증폭기에서 CPAR을 보상하기 위해 흔히 사용하는 기법이다. CF·RF = CPAR·RG로 설정하면 보상 감쇠기가 되어서 피드백 분할기가 모든 주파수로 동일한 감쇠를 일으키고 CPAR 문제를 해결할 수 있다. 하지만 이 곱셈들이 불일치하면 증폭기 통과 대역으로는 ‘융기(bumps)’를 일으키고, 응답으로는 ‘마루(shelves)’를 일으킨다. ‘마루(shelves)’는 저주파수 응답이 평탄했다가 f = 1/2π·CPAR·RG 부근에서 다시 평탄한 수준으로 변화하는 것을 말한다.

그림 5(d)는 비반전 증폭기의 등가 CPAR 보상을 보여준다. 주파수 응답을 분석해서 적절한 CF를 구해야 하며, 증폭기 대역폭을 이 분석에 포함시켜야 한다.

여기서 잠시 전류 피드백 증폭기(CFA)에 대해서 언급하려 한다. 그림 5(a)의 증폭기가 CFA라면 RIN이 주파수 응답을 조절하기 위해 큰 역할을 하지 못할 것이다. 이는 -입력이 아주 낮은 임피던스이고 동적으로 +입력을 복제하기 때문이다. 그러면 잡음이 다소 악화되고 VOS/RIN으로서 추가적인 -입력 바이어스 전류가 발생될 것이다.

마찬가지로 그림 5(b)의 회로 역시 RG로 인해서 주파수 응답이 변화되지 않을 것이다. 비반전 입력은 가상 접지일 뿐만 아니라, 접지에 대해서 낮은 임피던스이고 이미 CPAR을 허용할 수 있기 때문이다(비반전 모드만 해당됨). 또한 DC 오차는 그림 5(a)와 비슷할 것이다. 그림 5(c)와 (d)는 전압 입력 연산 증폭기에 사용하기 좋을 것이다. 하지만 CFA는 발진을 일으키지 않고서는 직접적인 피드백 커패시터를 허용하지 못한다.

부하 문제

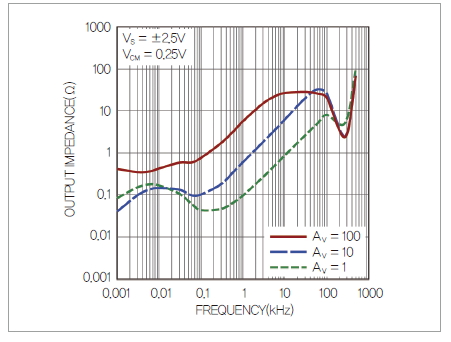

피드백 커패시턴스만 위상 마진을 깎는 것이 아니다. 부하 커패시턴스 역시 위상 마진을 깎을 수 있다. 그림 6은 각기 다른 이득 설정에 대해 LTC6268의 주파수에 따른 출력 임피던스를 보여준다.

그림 6. 3개 이득에 대한 LTC6268의 주파수에 따른 출력 임피던스

이를 보면 단위 이득 출력 임피던스가 더 높은 이득일 때의 출력 임피던스보다 낮다는 것을 알 수 있다. 최대 피드백은 개방 루프 이득이 증폭기 고유의 출력 임피던스를 낮출 수 있도록 한다. 그러므로 그림 6에서 이득 10의 출력 임피던스가 전반적으로 단위 이득보다 10배 더 높게 나타난다.

피드백 감쇠기에 의한 1/10 이득이 루프 이득을 감소시킨다. 그렇지 않으면 폐쇄 루프 출력 임피던스를 감소시킬 것이다. 개방 루프 출력 임피던스는 약 30Ω로서, 이득 100인 곡선 상에서 고주파수 대에서 평탄한 구역이 나타나는 것으로서 알 수 있다. 대략 GBF/100 지점에서부터 GBF 지점까지 이르는 이 구역에서는 루프 이득이 충분하지 않아 개방 루프 출력 임피던스를 감소시킨다.

커패시터 부하는 개방 루프 출력 임피던스와 함께 위상 및 진폭 지연을 일으킨다. 예를 들어 50pF 부하와 LTC6268의 30Ω 출력 임피던스는 106MHz에서 또 다른 극점을 일으킨다. 이 지점에서 출력은 -45° 위상 지연과 -3dB 감쇠를 겪는다. 이 주파수일 때 증폭기의 위상은 -295°이고 이득은 10dB이다. 단위 이득 피드백이라고 했을 때 위상이 ±360°(106MHz일 때)가 아니므로 발진을 일으키지 않는다. 하지만 150MHz일 때는 증폭기가 305° 지연에 5dB 이득이다.

또한 출력 극점은 위상이 -atan(150MHz/106MHz) = -55°이고 이득은 다음과 같다.

다시 말해 -4.8dB이다. 여기에 루프 이득을 곱하면 360°에 +0.2dB 이득이 됨으로써, 역시 발진을 일으킨다. 결국 50pF이 LTC6268의 발진을 일으키게 하는 최소 부하 커패시턴스인 것으로 나타난다.

부하 커패시턴스로 인해서 발진을 일으키지 않도록 하기 위한 가장 일반적인 방법은 간단하다. 피드백 배선 다음에 직렬로 낮은 값의 저항을 배치하면 된다. 10Ω에서 50Ω에 이르는 값을 사용해서 커패시티브 부하가 일으킬 수 있는 위상 지연을 제한할 수 있으며, 또한 아주 높은 속도일 때 증폭기를 낮은 커패시티브 임피던스로부터 차단시킬 수 있다.

하지만 이렇게 한다면 부하 측의 저항에 따라서 DC 및 저주파 오차를 일으키고, 커패시티브 부하에서의 주파수 응답을 제한할 수 있으며, 부하 커패시턴스가 전압에 대해서 일정하지 않을 때 신호 왜곡을 일으킬 수 있다는 단점이 있다.

부하 커패시턴스로 인해 발생되는 발진은 증폭기 폐쇄 루프 이득을 높임으로써, 방지할 수 있다. 증폭기를 더 높은 폐쇄 루프 이득으로 작동시키면 피드백 감쇠기 역시 루프 위상이 ±360°가 되는 주파수 지점에서 루프 이득을 감쇠시킨다. 예를 들어 LTC6268을 +10의 폐쇄 루프 이득으로 작동시키면, 이 증폭기는 40MHz에서 이득이 10V/V, 즉 20dB이고 이때 위상 지연은 285°이 된다. 발진이 일어나려면 출력 극점이 추가적인 75° 지연을 일으켜야 한다. 이 출력 극점은 다음과 같이 구할 수 있다.

-75° = -atan(40MHz/Fpole) → Fpole = 10.6MHz

이 극점 주파수는 500pF 부하 커패시턴스와 30Ω 출력 임피던스로부터 비롯되는 것이다. 출력 극점 이득은 다음과 같다.

언로드 된 개방 루프 이득이 10이면 발진 주파수일 때 루프 이득은 0.26이 된다. 그러므로 이때는 발진이 일어나지 않는다. 이에 폐쇄 루프 이득을 높여서 허용할 수 있는 부하 커패시턴스를 50pF에서 500pF으로 높였다.

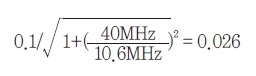

비종단 전송 라인 또한 악성 부하이다. 이는 주파수에 따라 반복적으로 거친 임피던스 및 위상 변동을 일으키기 때문이다(그림 7에서는 비종단 9’ 케이블의 임피던스를 보여줌). 증폭기가 한 저주파 공진 주파수로는 케이블을 안전하게 구동할 수 있다. 하지만 그보다 높은 주파수에서는 자체적인 위상 마진이 저하됨으로써 발진을 일으킬 수 있다. 그러므로 케이블을 비종단 해야 할 때는 출력과 직렬로 역매칭(back-match) 저항을 사용해서 케이블의 급격한 임피던스 변동을 차단할 수 있다. 뿐만 아니라 케이블의 비종단 단으로부터의 트랜션트 반사가 증폭기로 유입되더라도, 케이블의 특성 임피던스와 일치하기만 한다면 역매칭 저항이 이 에너지를 적절히 흡수할 수 있다.

그림 7. 비종단 동축 케이블의 임피던스 및 위상

또한 역매칭 저항이 케이블 임피던스와 일치하지 않는다면 일부 에너지가 증폭기와 종단으로부터 반사되어 다시 비종단 단으로 흘러 들어갈 수 있다. 이 에너지가 단에 가서 부딪힌 다음 또 다시 증폭기로 반사되고, 이런 식으로 매번 감쇠되면서 일련의 펄스들이 바운싱 될 수 있다.

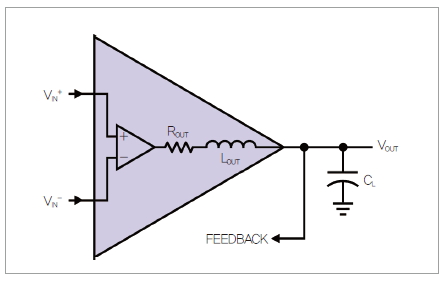

그림 8은 전체적인 출력 임피던스 모델을 나타준다. ROUT은 LTC6268에서와 같이 30Ω이고, 여기에 LOUT항을 추가하고 있다. LOUT은 물리적 인덕턴스와 전자적 등가 인덕턴스의 조합이다. 물리적 패키지, 본드 와이어 및 외부적 인덕턴스가 5nH∼15nH를 추가할 수 있으며, 더 소형 패키지일수록 이 인덕턴스는 작아진다. 여기에 더해서 대다수 증폭기는 20nH∼70nH에 이르는 인덕턴스를 포함한다. 특히 바이폴라 출력 소자를 사용하는 경우에는 더욱 그렇다.

그림 8. 증폭기 출력 임피던스의 인덕티브 부분

출력 트랜지스터의 기생 베이스 저항은 이들 소자의 유한한 Ft에 의해서 인덕턴스로 변환된다. 문제는 LOUT이 CL과 상호작용함으로써, 직렬 공진 공조 회로를 형성하고 ROUT이 루프로 조금 더 높은 위상 지연을 일으키지 않고서, 즉 발진을 일으키지 않고서는 구동할 수 없는 수준으로 임피던스가 떨어질 수 있다는 것이다. 예를 들어 LOUT = 60nH와 CL = 50pF으로 설정한다고 하자.

그러면 공진 주파수는 다음과 같다.

이를 통해 보면, LTC6268의 통과대역 이내이다. 이 직렬 공진 회로는 실제적으로 공진 시에 출력을 로드하고 공진 주파수 부근에서 루프 위상을 심각하게 변화시킨다. 안타깝게도 증폭기 데이터 시트에서는 LOUT에 대해서 언급하고 있지 않으나, 개방 루프 출력 임피던스 그래프에서 이 효과에 대해서 확인할 수 있다. 대체적으로 대역폭이 50MHz 미만인 증폭기에서는 이 효과가 중요한 문제가 아니다.

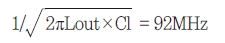

그림 9는 이 문제에 대한 해결책을 보여준다. RSNUB와 CSNUB를 사용해서 소위 스너버(snubber)라고 하는 것을 구현할 수 있다. 이의 용도는 공진 회로를 ‘de-Q’함으로써 증폭기 출력에서 아주 낮은 공진 임피던스를 나타내지 않도록 하는 것이다. RSNUB의 값은 통상적으로 공진 시에 CL의 리액턴스로 한다. 이 예에서는 -j35Ω이다.

그림 9. 출력 스너버 사용

이를 통해 출력 공진의 Q를 ∼1 이내로 낮출 수 있다. CSNUB의 크기는 출력 공진 주파수로 RSNUB를 최대로 삽입할 수 있을 정도로 한다. 다시 말해 CSNUB 리액턴스 << CL이 되도록 한다. CSNUB = 10·CL이면 적당하다. CSNUB는 중간 주파수 및 저주파수, 특히 DC일 때 증폭기에 영향을 미치지 않는다.

CSNUB가 매우 크면 중간 주파수 및 저주파수일 때, 증폭기가 RSNUB에 의해 심하게 로드되고 이득 정확도, 폐쇄 루프 대역폭 및 왜곡이 악화될 수 있다. 그럼에도 불구하고 스너버는 약간만 조정해도 리액티브 부하를 다루기에 유용할 수 있다. 다만 상황에 따라서 크기를 적정하게 해야 한다.

전류 피드백 증폭기의 -입력은 버퍼 출력이며, 그림 8의 직렬 특성을 나타낸다. 그러므로 출력과 마찬가지로 CPAR에 대항해서 자체적으로 발진을 일으킬 수 있다. 이에 CPAR과 연관된 인덕턴스를 최소화해야 한다. -입력에서는 스너버가 주파수에 대해서 폐쇄 루프 이득을 변화시키므로 유용하지 않다.

임피던스 이상

수 많은 증폭기는 높은 주파수일 때 입력 임피던스 이상(strange impedance)을 나타낸다. 특히 Darlington 구성과 같이 2개 입력 트랜지스터를 직렬로 사용하는 증폭기의 경우에는 더욱 그렇다.

또한 증폭기 중 대다수는 입력 상에서 npn/pnp 트랜지스터 쌍을 사용하며, 이 트랜지스터 쌍이 주파수에 걸쳐서 Darlington과 유사하게 동작한다. 일반적으로 GBF를 지난 특정 주파수 지점에서는 입력 임피던스의 실수 부분이 음(negative)이 될 수 있다.

인덕티브 소스 임피던스가 입력 및 보드 커패시턴스와 공진을 일으키고 음의 성분이 발진을 부추길 수 있다. 비종단 케이블로 구동할 때는 이 점이 또한 많은 반복적 주파수로 발진을 일으키게 할 수 있다.

입력 상에서 불가피하게 긴 인덕티브 라인을 사용해야 할 때는 몇 개의 직렬 에너지 흡수 저항들을 사용해서 분할하거나, 증폭기 입력 리드 상에 중간 정도 임피던스 스너버(약 300Ω)를 설치할 수 있다.

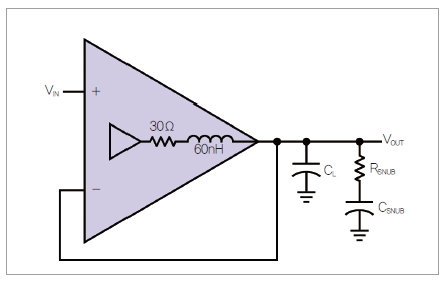

전원

발진을 일으킬 수 있는 요인으로서 마지막으로 고려해야 할 것은 전원 바이패스이다. 그림 10은 출력 회로의 일부를 보여준다. LVS+와 LVS-는 패키지, IC 본드 와이어, 바이패스 커패시터의 물리적 길이(여느 컨덕터와 마찬가지로 유도성)로 인한 불가피한 직렬 인덕턴스와 회로 보드 트레이스 인덕턴스이다.

그림 10. 전원 바이패스

만약 전원 플레인이 아니라면 로컬 바이패스와 전원 버스의 나머지 부분을 연결하는 바깥쪽 인덕턴스를 포함한다. 3nH∼10nH가 큰 것 같지 않아도, 200MHz일 때는 3.8Ω∼j12Ω이 된다. 그러므로 출력 트랜지스터가 높은 고주파 출력 전류를 전도할 때는 전원 인덕턴스 상에서 강하가 일어난다.

증폭기의 나머지 부분은 잡음이 없는 전원을 필요로 한다. 이는 주파수 전반에 걸쳐 전원을 제거할 수 없기 때문이다.

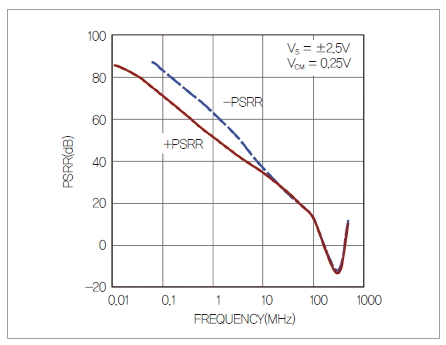

그림 11에서는 LTC6268의 주파수에 따른 PSRR(전원 전압 제거비, power supply rejection ratio)을 보여준다. 접지 핀이 없는 모든 연산 증폭기에서는 보상 커패시터가 전원과 연관됨으로써 증폭기로 전원 잡음을 결합시키므로 gm이 이를 막아낼 수 있어야 한다. 보상 때문에 PSRR이 1/f로 감소하며 130MHz를 지나서는 전원을 제거하는 것이 이득이 된다.

그림 11. LTC6268의 주파수에 따른 전원 제거비

200MHz에서 PSRR의 이득으로 출력 전류가 LVS 인덕터 내에서 전원 전압을 방해할 수 있다. 이는 PSRR 증폭을 통해서 강한 증폭기 신호가 되어서 출력 전류를 구동하고 내부적 전원 신호 등을 발생시킴으로써 증폭기가 발진을 일으키도록 한다.

바로 이러한 점 때문에 모든 증폭기의 전원을 인덕턴스가 낮은 트레이스 및 소자를 사용해서 신중하게 바이패스해야 하는 것이다. 더불어 전원 바이패스 커패시터를 어떤 부하 커패시턴스보다 훨씬 크게 해야 한다.

500MHz 부근의 주파수에서는 3nH∼10nH가 j9.4Ω∼j31.4Ω이 된다. 이 정도이면 출력 트랜지스터만으로도 인덕턴스와 IC 커패시턴스 내에서 발진을 일으키기에 충분히 높은 것이다. 특히나 출력 전류가 높을 때는 트랜지스터 gm과 대역폭이 증가한다. 오늘날 반도체 제조 프로세스는 대역폭이 아주 높은 트랜지스터를 채택하고 있으므로 각별한 주의를 기울여야 한다. 특히 출력 전류가 높을 때는 더욱 신경써야 한다.

결론

디자이너들은 연산 증폭기 단자에 따른 기생 커패시턴스 및 인덕턴스와 부하 특성을 고려해야 한다. 증폭기 제품들은 공칭 환경으로 안정적이도록 설계되지만, 각기 애플리케이션의 필요에 따라 적절히 분석하고 고려해야 한다.

<베리 하비(Barry Harvey) 리니어테크놀로지 디자인 엔지니어>