실리콘 제품 검정에 대해 전문적인 지식을 갖고 있는 TI에서는 GaN 검정에 이를 활용하고 있다.

여기에는 실리콘 검정 절차의 기원을 이해하는 기본 원리로 돌아가 GaN 고유의 장애, 활성 에너지, 가속 계수에

기초해 테스트를 만들 필요가 있다. 그리고 특별한 인덕티브 스위칭 테스트 방식으로 스트레스 테스트를 실시하고,

실제 제품 구성으로 부품을 실행시킴으로써 관련 애플리케이션에 맞춰 GaN을 검정해야 한다.

질화갈륨(GaN) 소재는 흥미롭고 파격적이며 새로운 전원 스위치 및 전원 GaN HEMT(High-Electron Mobility Transistor)를 가능하게 한다. HEMT는 온 저항이 매우 낮은(On-Resistance) FET(Field-Effect Transistor)이다. 이것은 비슷한 크기의 실리콘 전력 트랜지스터보다 더 빠르게 전환할 수 있으며, 이러한 장점은 전력 전환을 에너지 효율적, 공간 효율적으로 만들어준다. 또한 GaN은 실리콘 기판에서 성장시킬 수 있는데, 이 경우 실리콘 제조 역량은 높아지고 비용은 낮아진다. 그러나 새로운 기술을 사용할 때는 신뢰성이 입증돼야 한다. 여기서는 GaN 디바이스의 조건에 대해 살펴본다.

업계에서는 30년 간 사용해 왔으며 지속적으로 개선됐다는 점에서, 실리콘 전력 트랜지스터를 신뢰하고 있다. 오랜 경험이 검정 기법을 성숙하게 했고, 표준화된 테스트로 신뢰성 및 품질을 인증하고 있다. 이 테스트들은 장애 모드와 활성 에너지 및 가속 계수, 수명을 추론하기 위한 통계적, 수학적 프레임워크 개발, 그리고 고장률 및 결함 등을 이해하기 위한 정교한 노력에서 비롯된 것이다. 이 검정 기법이 충분히 입증됨에 따라 몇 세대에 걸쳐 실리콘 부품이 실제 사용 조건에서 진정한 수명 기간을 향상시켰다는 것을 나타낸다.

그러나 GaN 트랜지스터는 최근 개발된 것이다. 값비싼 실리콘 카바이드 기판의 RF GaN HEMT는 그 신뢰성이 입증된 무선 기지국에서 널리 쓰이고 있다.[1]

전원 GaN HEMT도 기본 원리가 비슷하지만 더 높은 전압을 취급할 수 있도록 기능들이 몇 가지 추가됐다. 이것은 실리콘 기판에서 생성하며 실리콘 제조 호환 소재를 활용함으로써 비용을 낮춘다.

또한 페일세이프(Fail-Safe)를 이유로 강화 모드(Enhancement-mode, e-mode) 또는 평상 시 오프 디바이스여야 한다. 여기에 주요 3가지 아키텍처가 있다.

① 소모 모드(Depletion-mode, d-mode) 절연 게이트 GaN HEMT와 캐스코드된 e 모드 Si FET

② e 모드 절연 게이트 GaN HEMT

③ p 중독, e 모드 접합 게이트 GaN HEMT

이들은 서로 다른 장애 모드를 갖고 있으며 실리콘 FET와도 다른 장애 모드를 갖고 있어 검정 방법에 대한 문제가 제기되고 있다.

표준 실리콘 기반 검정 방식은 훌륭한 품질 신뢰성 이정표이기는 하지만 디바이스의 수명, 고장률 및 애플리케이션과 관련된 적절성 차원에서 GaN 트랜지스터에게도 의미가 있는지는 명확하지 않다.

텍사스 인스트루먼트(TI)의 경우에는 FRAM(Ferroelectric Random Access Memory)과 같은 실리콘 이외의 기술을 포함해 신뢰할 수 있는 반도체 제품을 시장에 선보이고 있으며, 반도체 기술 산업 분야에서 오랜 역사를 갖고 있다. TI는 또한 GaN 관련 검정 기법과 애플리케이션 관련 테스트를 통해 신뢰할 수 있는 GaN 제품을 시장에 선보이고 있다.

표준 검정 기법

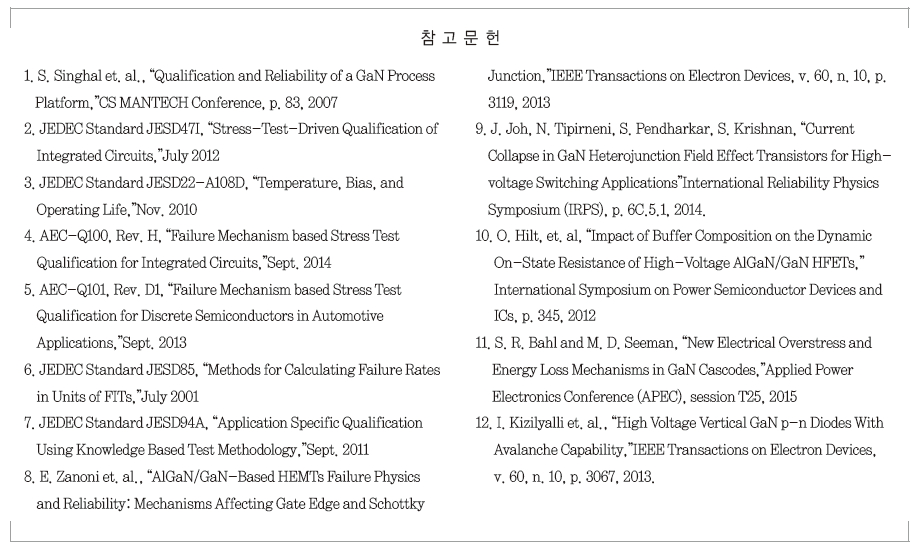

실리콘 전원 디바이스를 검정하는 표준 기구는 JEDEC(Joint Electron Device Engineering Council)와 AEC(Automotive Electronics Council)[2, 3, 4, 5] 두 곳이다. 이러한 표준들은 여러 테스트를 규정하고 있는데 ESD(Electrostatic Discharge), 패키지, 디바이스 등 3개의 카테고리로 나뉜다.

정전기 방전(ESD) 요건은 핸들링에 의해 도입되는 것이므로, ESD 검정은 변하지 않을 것으로 보인다. 패키징 테스트는 실리콘에서 실행되는 테스트와 유사할 것으로 예상되지만, 예상치 못한 장애 메커니즘에 집중해 장애를 근원까지 몰아붙여야 할 것이다. 유사점이 있는 이유는 패키지 스트레스, 본딩 표면의 상호작용과 같은 문제가 공통적이며, 지금까지 실리콘에서 사용된 백엔드 프로세싱이 GaN에서도 사용되기 때문이다. 하지만 디바이스 카테고리는 새로우며 더 중요하다. 이제부터는 표준 실리콘 검정 방식에 대해 살펴보고, GaN에 어떻게 응용할 수 있는지 알아본다.

실리콘 검정을 위해 1,000시간 동안 적어도 125℃ 이상의 접합 온도에서 표준 스트레스가 실시된다. 0.7eV 활성 에너지를 가정하고 온도 가속 계수를 78.6로 설정한다.[2] 그러면 125℃ 접합 온도(Tj)에서의 1,000h 스트레스는 Tj=55℃에서 9년간 사용하는 것과 같아진다.

디바이스는 최대 동작 전압에서 검정을 받는다. 개별 전력 FET의 경우, 일반적으로 최소 붕괴 전압 사양의 80%가 되도록 선택한다. 즉, 검정 테스트 조건에 어떤 전압 가속도 넣지 않고 온도만으로 가속을 달성한다는 뜻이다. 이는 전원 디바이스에서 중요한 의미를 갖는다. Tj는 55℃보다 높은, 75℃ 이상인 경우가 일반적이기 때문이다.

이 표준은 3개의 로트(lot)가 각각 77개의 부품을 가지며 스트레스를 부여했을 때 장애가 없어야 한다고 규정하고 있다. 231개 중 장애가 하나도 없어야 한다는 기준은 LTPD(Lot-Tolerant Percent Defective) 값이 1이라는 뜻이다.[2] 즉, 이것은 추정되는 스트레스 조건에서 90% 신뢰도로, 한 로트의 부품 하자가 1% 미만이라고 할 수 있다. 다시 말해, 최대 동작 전압 편성으로 Tj=55℃에서 9년 동안 사용한다는 뜻이다.

Tj=55℃에서 약 50 FIT(Failure in Time)라는 초기 최대 FIT 비율도 0.7eV 활성 에너지를 사용해 231개 유닛 중 제로 고장(Zero Fails)이라는 결과에서 나온 것이다.[6]

이 정적 테스트 외에 동적 테스트도 있다. 이것은 “디바이스를 동적 운전 모드에서 작동시킬 수 있다”라고 어설프게 규정되어 있다.[3]

이 테스트를 규정하는 것은 제조사의 몫이다. 따로 규정된 테스트가 없는 이유는, 끊임없이 진화하는 애플리케이션과 기술에 부합하는 테스트를 규정해두기 어렵기 때문이다. 규정된 스트레스 테스트는 실제 사용 환경과 별로 관련 없을 수도 있고, 거짓 장애나 고장을 만들어 유효 장애 메커니즘을 가속시킬 수도 있다.[7]

실리콘 FET의 경우, 검정 기법의 신뢰도는 오랜 세월 실제 사용에 의해 확립된 것이다. 이에 반해 GaN과 같은 새로운 기술은 디바이스 제조사가 실제 사용을 예측하는 동적 테스트를 규정하게 된다.

따라서 애플리케이션 관련 스트레스 테스트를 개발해 실제 사용 조건에서 신뢰성을 검증할 수 있어야 한다.

마지막으로 GaN은 전자적으로 견고하지 않다는 우려가 있다. 다시 말해, 디바이스를 붕괴까지 몰아붙이면 손상을 입게 될 것이라는 뜻이다. 이 문제는 특히, PFC(Power Factor Correction) 회로와 같은 고전압 애플리케이션에서 다루어져야 한다. 이 경우에는 전력선의 번개 스파이크와 같은 과전압 이벤트에 디바이스가 노출되는 경우를 말한다.

표준 검정 기법의 변용

JEDEC 표준과 AEC 표준 모두 튼튼한 기본 원칙에 근거하고 있지만, 기술 도입을 늦춘다. 실리콘 검정을 통과한다는 것은 훌륭한 징표이긴 하지만, 고객은 실제 사용 조건에서 낮은 고장률로, 예컨대 10년이라는 수명기간 동안 지속적으로 사용할 수 있는 제품을 필요로 한다. 따라서 FRAM, 스케일드 CMOS, GaN과 같은 신기술을 도입하는 기업들은 이 표준의 기원이 된 기본 원리를 이해해야 한다.

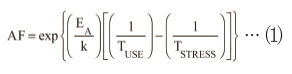

JEDEC 검정 기법에서는 주된 촉매가 온도이다. 가속 계수(AF)는 식 (1)에 따라 계산된다. 여기서 EA는 활성 에너지이고, k 는 볼츠만(Boltzmann) 상수이다.

식 (1)을 스트레스 온도 Tj=125℃, 사용 온도 Tj=55℃, 활성 에너지 약 0.7eV에서 사용할 경우, 가속 계수는 78.6이 된다. Tj=125℃에서의 1,000h 스트레스가 Tj=55℃에서 10년 사용했을 때와 거의 비슷한 이유가 이 때문이다. 참고 문헌에 따르면, GaN의 활성 에너지[8]는 1.05∼2.5eV이다.

이와 같이 넓은 범위 값은 세계 여러 곳의 서로 다른 실험실과 기업들이 다양한 디바이스, 프로세스 및 소재를 사용하고 있다는 것을 의미한다. 이러한 범위는 가속 계수의 변량을 넓힐 수 있다. 즉, EA=1.05eV에서 687부터 EA=2.5eV에서 500만 이상까지 변량이 커질 수 있다.

따라서 완제품을 대표할 수 있는 프로세스 및 디바이스 아키텍처에서 활성 에너지를 확정해야 한다.

또한 실제 동작하는 접합 온도도 고려해야 한다. 넓은 밴드갭 때문에, GaN은 실리콘보다 높은 온도에서 작동하는데, 이것은 전원 전자제품에서 중요한 요소이다. 그리고 디바이스를 검정할 때는 몇 가지 계수를 고려해야 한다.

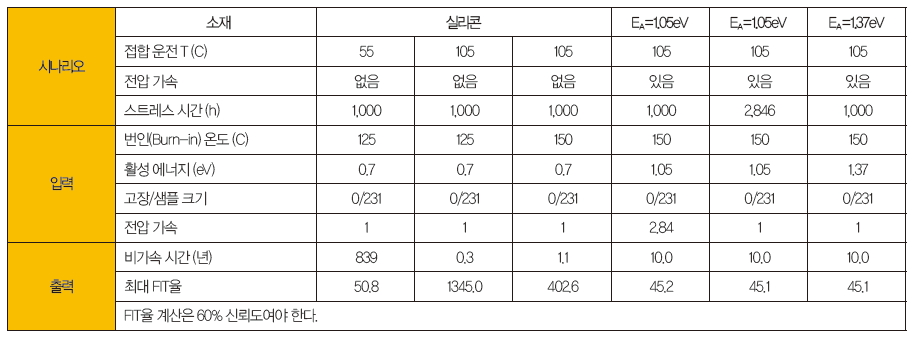

표 1은 125℃에서의 표준 1,000h 실리콘 검정 스트레스를 다른 몇 가지 시나리오들과 비교해 나타낸 것이다.

표 1. 여러 스트레스 파라미터들이 신뢰성 및 품질 추정에 미치는 영향

접합 동작 온도(Tj) 105℃를 원할 경우, 활성 에너지를 0.7eV라고 가정하면 비가속 시간이 약 9년에서 0.3년으로 떨어진다는 것을 알 수 있다. 스트레스 온도를 150℃로 높이면 이 시간을 1.1년까지 증가시킬 수 있다. 이것은 표준 패키지에 있어서는 실질적인 범위이다.

이 경우의 스트레스 테스트는 필드에 상응하는 수명을 충족시키거나 약 50 FIT라는 최대 FIT 비율 조건을 해결하지 못한다. 하지만 신뢰성 및 품질의 징표 역할은 할 수 있다.

10년 동안의 사용을 대표하는 1,000h 스트레스는 87.6의 가속 계수가 필요하며, 1.37의 활성 에너지에서 달성된다. 이보다 낮은 활성 에너지, 예를 들어 레퍼런스[8]보다 낮은 1.05eV는 2.84배의 전압 가속이 필요하거나 약 6주에서 17주로 기간 연장이 필요해진다.

과도한 전압 가속은 대표성이 떨어지는 장애 모드를 불러올 수 있고, 기간 연장은 신제품 개발 사이클을 연장시킬 수 있다. 장애 모드와 패키지의 가용 가속에 따라 필요한 필드 상응 수명기간을 대표하는 검정 테스트가 불가능해질 수 있다.

수명 요건은 웨이퍼 레벨의 신뢰성 테스트[2]로 확보하고, 패키지 부품에 대한 연장 기간 스트레스 테스트를 실시해 검증해야 한다.

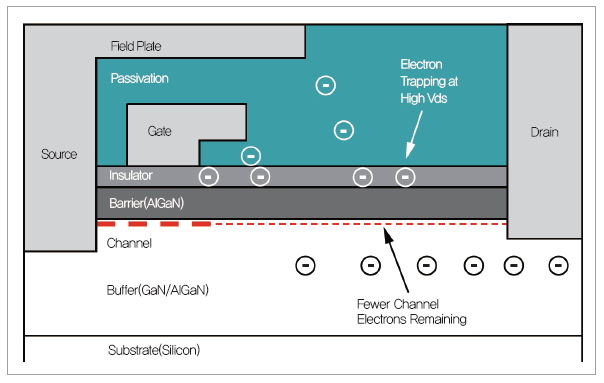

장애 기준은 구체적인 GaN 장애 모드에 근거해야 한다. 동적 Rds-on(온) 상승은 특별한 장애이며, 전류 붕괴(Current-Collapse)라고도 한다. 이것은 음전하가 버퍼와 톱사이드 레이어 둘 다에 갇혔을 때 일어난다.[9,10] 전하는 고전압이 적용될 때 갇힐 수 있으며, 디바이스를 켰을 때 즉시 소멸하지 않을 수 있다.

갇힌 음전하는 채널 레이어의 전자를 밀어내고, 채널 레이어의 전자 숫자가 감소해 Rds 온이 상승한다(그림 1). 나중에 갇힌 전하가 소멸되면 Rds-on이 회복된다. 이로 인해 효율이 떨어지고, 그러면 디바이스가 과도하게 자기 발열하게 되어 정상보다 빨리 고장날 수 있다.

그림 1. GaN 디바이스의 단면도는 갇힌 전자가 채널 레이어의 전자 숫자를 감소시켜 Rds 온을 상승시킨다는 것을 보여준다

또한 디바이스가 노후되면 트랩 밀도가 상승해 동적 Rds 온 효과가 악화될 수 있다. TI는 스트레스 테스트를 실시하는 동안 동적 Rds 온을 감시할 수 있는 특수 하드웨어를 보유하고 있으므로 이러한 문제 없이 제품을 출시할 수 있다.

애플리케이션 관련 테스트

DC 테스트는 많은 수의 부품을 테스트하는 데 비교적 용이하긴 하지만, 실제 애플리케이션에서 GaN이 10년의 수명을 갖게 될지는 예측하지 못한다. 하드 스위칭 스트레스는 DC 스트레스와 다르다.

하드 스위칭된 전원 컨버터는 인덕티브 스위칭 과도를 갖게 된다. 이때 디바이스는 고전류와 고전압에 동시에 노출된다. 턴 온 과도의 경우 스트레스가 가장 많다. 드레인 전압 Vds가 떨어지기 전에 FET 채널이 풀 인덕터 전류를 가라앉혀야 하고, 그 노드에서 다른 디바이스들의 역회복을 해제시켜야 하기 때문이다.

또한 이것은 Vds가 떨어질 경우, 디바이스의 출력과 스위칭된 노드 커패시턴스의 해제에서 비롯된 추가 전류를 운반해야 한다. 그러나 턴 오프는 스트레스가 적은 편인데, Vds가 낮을 때 FET 채널이 꺼지고 인덕터 전류가 해당 커패시턴스 충전에 돌입하기 때문이다.

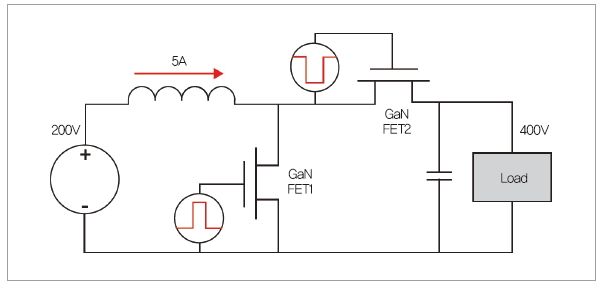

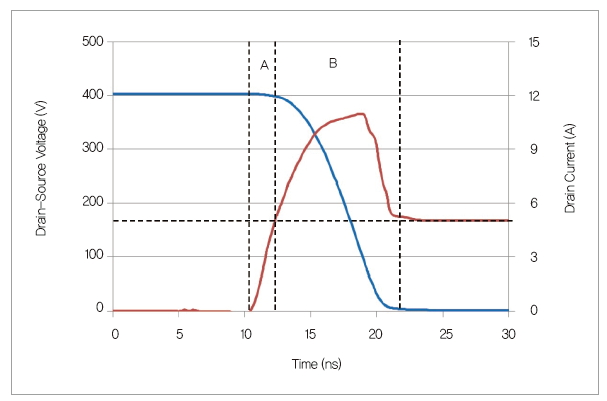

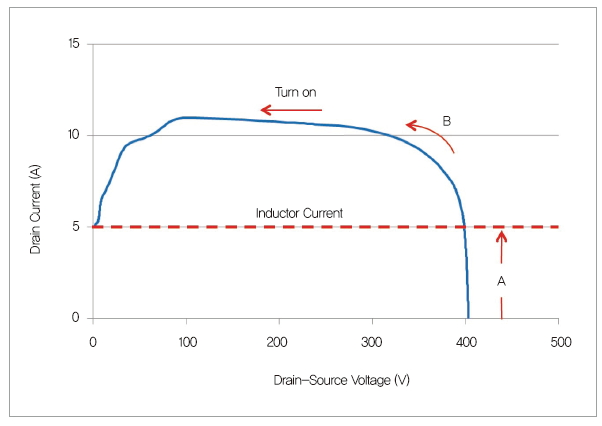

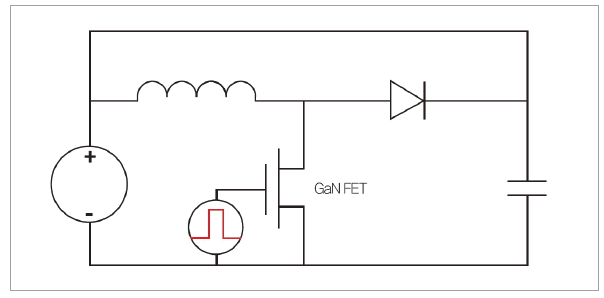

디바이스 스트레스는 그림 2에 나타난 토폴로지의 부스터 컨버터를 이용해 설명한다. 프라이머리 스위치(FET1)에서 하드 스위칭 턴온 과도의 시뮬레이션 결과는 그림 3을 참고한다. 입력 전압은 200V이고, 인덕터 전류는 5A(로드 전류는 약 2.5A)다. 이 경우, FET1이 꺼지면 그 드레인 전압은 약 400V에서 고정된다. 클램프 FET(FET2)의 전도 때문이다. 그 결과 FET1이 켜졌을 때, VdS가 강하를 시작하기 전에 풀 인덕터 전류를 가라앉혀야 한다(A 영역).

드레인 전압이 떨어지면(B 영역), FET는 스위칭된 노드에서 커패시턴스를 방출해야 한다. 이것은 클램프 FET와 보드 트레이스, 기타 연결 컴포넌트에서 비롯된다. 이 클램프에는 역회복 전류가 없는데, 그 이유는 GaN FET를 사용하기 때문이다.

V-I 궤적(그림 4)은 높은 Vds에서 상당한 드레인 전류를 나타내고 있다. 이 경우에는 인덕터 전류값보다 약 6A 높다. 실제로 FET 채널 전류가 더 높은 이유는 FET의 드레인 커패시턴스가 이 채널을 통해서 방출하기 때문이다. 예를 들어, 50pF의 드레인 커패시턴스와 60V/ns 슬루율은 다시 3A를 추가시킨다.

그림 2. 간단한 부스트 컨버터 토폴로지

그림 3. 하드 스위칭된 이행을 위한 턴온 이행

그림 4. 인덕티브 스위칭 과도의 V-I 궤적은 높은 드레인 바이어스에서 상당한 전류 흐름을 보여준다. FET 드레인 커패시턴스의 방출은 채널 전류를 추가시킨다(예를 들어 50pF은 60V/ns에서 3A를 추가시킨다)

하드 스위칭을 실행하는 동안의 FET 채널 전류 흐름은 높은 Vds에서 커다란 핫 캐리어(Hot Carrier)를 발생시키므로 디바이스가 튼튼해야 한다. 또한 대형 디바이스 어레이의 경우 균일하지 않은 스위칭이 일어날 수 있고, 이는 디바이스 전류를 처음 켜지는 어레이 부분에 로컬 레이팅 초과로 밀어 넣을 수 있다.

높은 dv/dt 스위칭 역시 커패시티브 전류를 터미네이션과 같은 원치 않는 디바이스 영역에 유입시킬 수 있다. 신뢰성 테스트는 디바이스가 하드 스위칭 애플리케이션에도 충분히 튼튼하도록 실시해야 하며, 신뢰할 수 있는 스위칭 SOA(Safe Operating Area)가 디바이스의 고객 사용 조건을 충족하도록 실시해야 한다.

TI는 하드 스위칭 견고성을 검증하기 위해 단순 부스트 컨버터에 기반하여 인덕티브 스위칭 셀을 개발했다(그림 5). 선택은 다음과 같은 JEDEC의 권고에 따른 것이다.[7]

그림 5. 인덕티브 스위칭 애플리케이션 테스트를 위한 테스트 방식

실제 제품 복잡도가 본질적인 장애 메커니즘을 가릴 수 있으므로 관련 장애 모드 및 메커니즘에 따라 테스트 방식을 선택할 수 있다.

GaN FET가 꺼지면, 인덕터 전류가 다이오드를 통해 다시 입력으로 순환된다. 그러면 부하 레지스터가 필요하지 않게 되어 에너지를 절약할 수 있다. 이 셀은 연속 전류 모드에서 인덕터와 함께 실행된다. 스위칭 과도가 목적이므로 짧은 듀티 사이클을 이용해 에너지를 절약할 수 있다. 이 셀은 디바이스에 적용되는 전압, 전류, 주파수 및 온도를 변화시킬 수 있다. 추가 드레인 전류(그림 4)는 다이오드 커패시턴스가 제공한다.

추가 커패시턴스는 필요한 만큼 추가할 수 있다. 또한 이 셀은 스위칭 과도 1마이크로초 후에 디바이스의 동적 온저항(dRds-on)을 측정할 수 있는 하드웨어를 갖고 있다. 이와 같은 원위치 모니터링 기능이 필요한 이유는 온저항이 스트레스로 인해 악화돼 더 높은 전도 손실과 낮은 효율을 초래할 수 있기 때문이다.

제품에서 상승하는 온저항은 과도한 디바이스 자기 발열을 일으켜 열 고장을 일으키게 된다. ‘풀 포인트(Pull Point)’ 시점에서 스트레스를 중단시키면 온저항 하락이 회복되기 때문에 이와 같은 데이터를 얻을 수 없다. 그러므로 이 결정적인 GaN 장애 파라미터를 감시할 수 있어야 문제 없이 제품을 출시할 수 있다.

인덕티브 스위칭 테스트 외에도, GaN 멀티칩 모듈을 시스템에서 평가하고 실제 제품 사용 조건에서 실행시켜야 한다. 이것은 다른 시스템 부품과의 상호작동성을 검증하고, 알 수 없는 장애 메커니즘에 노출시키기 위한 것이다. 부품들은 개별적으로는 신뢰할 수 있더라도 상호작동할 때는 예상치 못한 방식으로 작동할 수 있다.

예를 들어, 캐스코드 GaN 디바이스의 경우, GaN 디바이스의 드레인 소스 커패시턴스를 통해 커플링된 전하가 턴오프 과도 과정에서 실리콘 캐스코드 디바이스에 전자사태를 일으킬 수 있다.[11] 이 디바이스도 부하 상태에서 실행돼 까다로운 열 조건 하에서 작동을 검증 받는다.

전자사태 견고성 문제에 대해서는 특별히 관심을 가져야 한다. 현재 GaN HEMT는 전자사태 성능을 보여주지 못하고 있다. 이것은 기술이 성숙됨에 따라 개선될 수 있는데, GaN 자체가 전자사태 기능을 갖고 있기 때문이다.[12] TI는 그동안 과전압 조건을 처리할 수 있을 만큼 충분히 여지를 두고 제품을 설계할 수 있다. 예를 들어, PFC 애플리케이션의 경우, 번개가 전력선을 때리면 FET에서 보이는 전압이 일시적으로 700V까지 상승할 수 있다. 이러한 애플리케이션을 위해 적어도 750V 이상의 스파이크를 견딜 수 있도록 GaN 디바이스를 제작해야 한다.

Sandeep R. Bahl _ 텍사스 인스트루먼트